Cadence Design Systems, Inc. anunció que varias de sus herramientas de desarrollo de sistema en chip han obtenido la versión 0.1 del manual de reglas de diseño (DRM) y la certificación de herramienta modelo SPICE para el proceso FinFET de 16 nanómetros de TSMC. La finalización de los primeros hitos de calificación de herramientas significa que los clientes de nodos avanzados pueden comenzar el desarrollo del diseño y aprovechar el bajo consumo de energía y el alto rendimiento requerido para las plataformas móviles de próxima generación.Cadence Design Systems, Inc. anunció que varias de sus herramientas de desarrollo de sistema en chip han obtenido la versión 0.1 del manual de reglas de diseño (DRM) y la certificación de herramienta modelo SPICE para el proceso FinFET de 16 nanómetros de TSMC. La finalización de los primeros hitos de calificación de herramientas significa que los clientes de nodos avanzados pueden comenzar el desarrollo del diseño y aprovechar el bajo consumo de energía y el alto rendimiento requerido para las plataformas móviles de próxima generación.

Esta cualificación de la herramienta sirve como base para la infraestructura de diseño de la tecnología FinFET de 16 nanómetros. Las herramientas de Cadence® certificadas son Spectre, Liberate, Virtuoso®, el sistema de implementación digital (EDI) Encounter®, el sistema de cronometraje de Encounter, el sistema de alimentación Virtuoso, el sistema de alimentación de Encounter, el sistema de verificación física y la extracción de QRC. Varios productos Cadence Design IP también están disponibles para chips de prueba de clientes en este nodo avanzado.

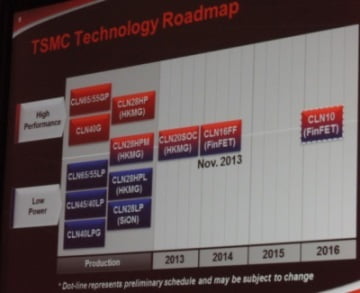

Además, TSMC ha calificado un flujo de diseño Cadence listo para producción en un proceso de fabricación de 20 nanómetros. Los clientes ahora pueden aprovechar al máximo las soluciones de Cadence para obtener los beneficios de velocidad, potencia y área de este nodo avanzado.

La cadena de herramientas completa tiene calificación de 20 nanómetros a través del diseño del procesador ARM® Cortex®-A9 y es la primera calificación de herramienta integrada para la tecnología de proceso TSMC 20SoC. Las herramientas de cadencia utilizadas son Virtuoso, Sistema EDI, Sistema de cronometraje de encuentro, Sistema de potencia de encuentro, Sistema de potencia Virtuoso, Sistema de verificación física y Extracción de QRC.

Chi-Ping Hsu, Ph.D., vicepresidente senior de investigación y desarrollo, Silicon Realization Group, Cadence. “La certificación de TSMC para Cadence Tools para diseños FinFET de 16 nanómetros y 20 nanómetros subraya nuestro compromiso conjunto de trabajar con nuestros clientes para garantizar su éxito”.

“Nuestra certificación DRM & SPICE inicial, lograda a través del modelo de colaboración Open Innovation Platform® de TSMC, es un testimonio de nuestra confianza en el uso de estas herramientas Cadence para el desarrollo temprano de diseños FinFET de 16 nanómetros de bajo consumo y alto rendimiento. ”, dijo Suk Lee. , Director sénior de la división de marketing de infraestructura de diseño de TSMC. “Y la certificación de Cadence Tools para 20SoC demuestra la preparación de la empresa para este proceso de tecnología avanzada”.

El anuncio de hoy complementa el primer procesador ARM Cortex-A57 de 64 bits implementado con tecnología FinFET, también desarrollado con Cadence Technology. Cadence y TSMC también anunciaron recientemente una asociación en 16 nanómetros.