El GTL1655 es un transceptor de bus de 16 bits que incorpora una impedancia de salida BAJA (100 mA/12 Ω) impulsada ALTA con traducción de nivel lógico LVTTL a GTL/GTL+ y GTL/GTL+ a LVTTL.

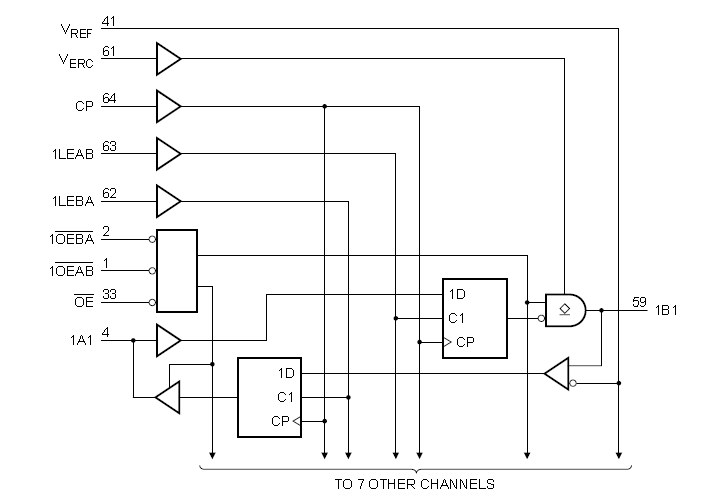

El dispositivo está configurado como dos transceptores de 8 bits que comparten un reloj común y un pin de habilitación de salida maestra, pero con sincronización de bloqueo y señales de habilitación de salida separadas. Los flip-flops tipo D y los pestillos tipo D permiten tres modos de transferencia de datos. Reloj, bloqueado o transparente. El GTL1655 proporciona una interfaz ideal entre tarjetas que funcionan a niveles LVTTL y backplanes que utilizan niveles de señal GTL/GTL+. La combinación de oscilación de salida reducida, niveles de umbral de entrada reducidos y control de borde configurable permiten el funcionamiento a alta velocidad de los backplanes GTL/GTL+.

El GTL1655 se puede utilizar con niveles de señal GTL (VTT= 1,2 V, VREF= 0,8 V) o GTL+ (VTT= 1,5 V, VREF= 1,0 V). El puerto A y las entradas de control cumplen con el nivel de señal LVTTL y toleran 5 V. El puerto B está diseñado para operar con niveles de señal GTL o GTL+, con VREF proporcionando la entrada de voltaje de referencia.

Los pines de habilitación de bloqueo (nLEAB y nLEBA), los pines de habilitación de salida (nOEAB, nOEBA) y el pin de reloj (CP) se utilizan para controlar el flujo de datos a través de dos transceptores de 8 bits (n = 1 o 2). Cuando nLEAB se establece en ALTO, el dispositivo funciona en modo transparente desde el puerto A al puerto B. Una transición de ALTO a BAJO en nLEAB bloquea los datos A independientemente de CP ALTO o BAJO (modo de bloqueo). Cuando nLEAB está en BAJO (modo de reloj), una transición de BAJO a ALTO en el CP sincroniza los datos A en el puerto B. Los pines de control nLEBA, nOEBA y CP se pueden usar de manera similar para controlar el flujo de datos del puerto B al puerto A. Todos los pines de E/S se pueden desactivar usando el pin OE.

Para optimizar la integridad de la señal, el GTL1655 cuenta con control de velocidad de borde ajustable (VERC). Al ajustar VERC entre GND y VCC, el diseñador puede ajustar la tasa de borde del puerto B para que coincida con las condiciones de carga de la aplicación.

El GTL1655 permite una verdadera capacidad de inserción en vivo al incorporar:

* BIAS VCC, precarga la salida para evitar perturbar los datos activos cuando se inserta la tarjeta.

* Ioff deshabilita el flujo de corriente a través de las E/S que están apagadas.

* Tristate en el encendido. Garantiza que las salidas sean de alta impedancia en el momento del encendido, lo que evita problemas de contención de bus. Cuando VCC supera los 1,5 V, el circuito de tres estados de encendido cede el control de la salida al pin OE. El pin OE debe conectarse a VCC a través de una resistencia pull-up para garantizar que la salida permanezca triestable.

*Características y Beneficios*

* Combinación de pestillos tipo D y flip-flops tipo D para la operación del transceptor en modo sincronizado, bloqueado o transparente

* Traducción de nivel lógico entre señales LVTTL y GTL/GTL+

* ALTA impedancia de salida BAJA del variador (100 mA/12 Ω) en el puerto B

* Los tiempos de subida y bajada del puerto B son configurables

* Admite inserción en vivo (Ioff, power-up tri-state, BIAS VCC)

* Retención de bus para la entrada del puerto A

* Tolerancia de sobretensión del puerto A

* Minimice el ruido de conmutación mediante el uso de pines VCC y GND distribuidos.

* Disponible en paquete TSSOP64

* Rango de temperatura industrial (-40°C a +85°C)

* Protección ESD

** HBM EIA/JESD22-A114-A supera los 2000 V

** CDM EIA/JESD22-C101 supera los 1000 V

* Cierre EIA/JEDS78 >200 mA