La macro XAUI de Fujitsu es para ASIC que realizan comunicaciones de datos de gran ancho de banda. Esta macro tiene un consumo de energía de 100 mW/canal (incluidos Rx, Tx, CDR, circuito de polarización y PLL, preénfasis máximo), 1,2 ± 0,10 C, suministro de 2,5 V ± 0,20 V y temperatura de unión de 0 °C que funciona con ~125°C.La macro XAUI de Fujitsu es para ASIC que realizan comunicaciones de datos de gran ancho de banda. Esta macro cumple con las siguientes especificaciones de fluctuación de XAUI.

* Jitter generación 0.60UI (jitter total de pico a pico)

* Cumple con los requisitos de máscara de tolerancia de fluctuación de fase sinusoidal

Esta macro tiene un consumo de energía de 100 mW/canal (incluidos Rx, Tx, CDR, circuito de polarización y PLL, preénfasis máximo), 1,2 ± 0,10 C, suministro de 2,5 V ± 0,20 V y temperatura de unión de 0 °C que funciona con ~125°C.

Esta macro está fabricada con la tecnología CMOS estándar de 0,11 µm de Fujitsu. Las macros se pueden utilizar en muchas aplicaciones diferentes.

*Ethernet 10G

* Enrutador WAN o plano posterior del interruptor y tarjeta de línea para cambiar la interfaz de estructura

* Línea de backplane de velocidad de datos x4 de 3,125 Gbps.

*característica*

* Tasa de transferencia de datos unidireccional de 3.125 Gbps x4 canales de capa física Ethernet 10G

*Cumple con la capa física IEEE802.3ae

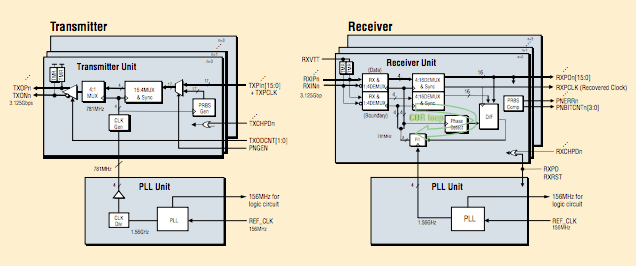

* Reloj de referencia de entrada de 156 MHz e interfaz paralela

* CDR Rx de 4 canales y matriz Tx de 4 canales

* Diferencial PCML (Vtem = 1,2 V y 1,8 V)

* Interfaz diferencial acoplada a CA

* SERDES 1:16 con caja de cambios 16:20, codificación 8B/10B y alineación de carril proporcionada como RTL/netlist

* Resistencia de terminación de 50 Ω integrada en el chip

* CDR basado en PLL de bucle dual independiente para cada canal Rx

* Generador y comparador PRBS (2^23-1) incorporado para pruebas de loopback

* Fuente de alimentación de 1,2 V y 2,5 V, proceso CMOS estándar de 0,11 μm

*ventaja*

* Disponible como celdas de biblioteca para diseños ASIC

* Oscilación de voltaje Tx programable y cantidad de pre-énfasis

* La ecualización Tx basada en pre-énfasis permite una pérdida de alta frecuencia de hasta 12 dB

* Cumple con la especificación de fluctuación de fase XAUI