Synopsys anunció que ofrece una solución integral de diseño 3D-IC incluida en el flujo de referencia CoWoS™ (Chip on Wafer on Substrate) de TSMC. Este flujo de diseño es el resultado de la última colaboración de las dos empresas en tecnología de integración 3D-IC. Proporciona una transición suave del circuito integrado (IC) tradicional “2D” a los flujos de diseño de apilamiento de múltiples matrices. Para respaldar el flujo de referencia de TSMC CoWoS, Synopsys ha lanzado una versión mejorada de las herramientas de la plataforma de implementación Galaxy para la implementación física, la extracción parásita, la verificación física y el análisis de tiempo. Los nuevos flujos y las mejoras en las herramientas ayudan a los ingenieros a ser más productivos y a reducir el tiempo de implementación. Acelere el tiempo de comercialización y el tiempo de producción en volumen al diseñar sistemas de matriz múltiple para el silicio CoWoS de TSMC.

Synopsys anunció que ofrece una solución integral de diseño 3D-IC incluida en el flujo de referencia CoWoS™ (Chip on Wafer on Substrate) de TSMC. Este flujo de diseño es el resultado de la última colaboración de las dos empresas en tecnología de integración 3D-IC. Proporciona una transición suave del circuito integrado (IC) tradicional “2D” a los flujos de diseño de apilamiento de múltiples matrices. Para respaldar el flujo de referencia de TSMC CoWoS, Synopsys ha lanzado una versión mejorada de las herramientas de la plataforma de implementación Galaxy para la implementación física, la extracción parásita, la verificación física y el análisis de tiempo. Los nuevos flujos y las mejoras en las herramientas ayudan a los ingenieros a ser más productivos y a reducir el tiempo de implementación. Acelere el tiempo de comercialización y el tiempo de producción en volumen al diseñar sistemas de matriz múltiple para el silicio CoWoS de TSMC.

dijo John Chilton, vicepresidente senior de marketing y desarrollo corporativo de Synopsys. “La tecnología de integración 3D-IC ofrece beneficios claros para los equipos de diseño que buscan lo último en rendimiento, el factor de forma más pequeño y el menor consumo de energía”. ha demostrado ser un complemento clave para el escalado tradicional de transistores de la “Ley de Moore” en muchas áreas de aplicación. La contribución de Synopsys al flujo de referencia de TSMC CoWoS permite a los diseñadores realizar rápidamente sistemas innovadores y avanzados de múltiples matrices. ”

Suk Lee, director sénior de marketing de infraestructura de diseño en TSMC, dijo: “La combinación de las herramientas EDA de Synopsys y la tecnología CoWoS de TSMC proporciona a los diseñadores respuestas productivas a la capacidad de fabricación de sistemas de matrices múltiples que optimizan el rendimiento y el consumo de energía”.

La plataforma de implementación Galaxy de Synopsys incluye compatibilidad con las tecnologías y los flujos de referencia CoWoS de TSMC. TSMC validó las herramientas de implementación, análisis y aprobación de Synopsys, que incluyen:

implementación física

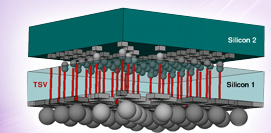

- Implementación física multi-die de IC Compiler™. Compatibilidad con la colocación, asignación y enrutamiento de microprotuberancias, a través de vías de silicona (TSV), almohadillas de sonda y C4. Las celdas de impacto combinadas permiten una asignación de impacto simplificada y flexible. Comprobación de alineación de microgolpes.Capa de redistribución (RDL) y enrutamiento de señales, y creación de Power Mesh en la capa de interconexión de CoWoS

Análisis y Aprobación

- Verificación de conectividad entre troqueles apilados con Hercules Layout vs. Schematic (LVS)

- El metal de enrutamiento de señal para TSV, microbump, RDL y CoWoS se interconecta con soporte de extracción parasitaria StarRC™ Ultra

- Análisis de tiempo PrimeTime® para sistemas de matrices múltiples

disponibilidad

La solución 3D-IC de Synopsys está actualmente disponible para un número limitado de clientes. Para obtener más información sobre las soluciones Synopsys 3D-IC, visite www.synopsys.com/3D-IC.