El conjunto de chips DS92LX1621 / DS92LX1622 proporciona una interfaz Channel Link III con un canal directo de alta velocidad y un canal trasero dúplex completo para la transmisión de datos a través de un solo par diferencial. Un par de serializador/deserializador está diseñado para una conexión directa entre un sistema de cámara automotriz y un controlador de host/unidad de control electrónico (ECU). El transporte principal transporta datos de imagen de 16 bits a través de un único flujo en serie de alta velocidad junto con un transporte de canal de control bidireccional de baja latencia compatible con I2C. La carga útil de 16 bits incluye opciones de integridad de datos seleccionables de CRC (comprobación de redundancia cíclica) o bits de paridad para controlar los errores del enlace de transmisión. La tecnología de reloj integrada de National permite una comunicación full-duplex transparente sobre un solo par diferencial, lo que permite que la información de control bidireccional asimétrica se transmita independientemente del intervalo de borrado de video. Este flujo serial único elimina los problemas de sesgo entre las rutas de datos paralelas y las rutas de reloj, lo que simplifica la transferencia de buses de datos anchos a través de pistas y cables de PCB. Esto reduce la ruta de datos, reduce las capas de PCB, el ancho del cable, el tamaño del conector y los pines, lo que genera un ahorro significativo en los costos del sistema.

Serializador y deserializador de enlace de canal balanceado III de CC de 10-50 MHz con canal de control bidireccional

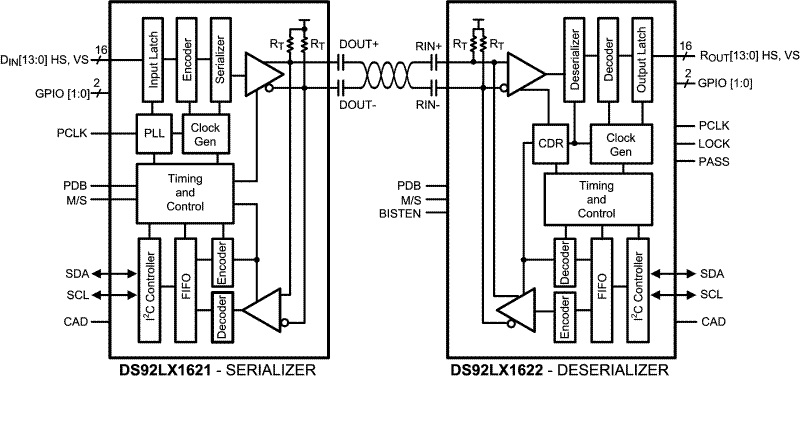

El conjunto de chips DS92LX1621 / DS92LX1622 proporciona una interfaz Channel Link III con un canal directo de alta velocidad y un canal trasero dúplex completo para la transmisión de datos a través de un solo par diferencial. Un par de serializador/deserializador está diseñado para una conexión directa entre un sistema de cámara automotriz y un controlador de host/unidad de control electrónico (ECU). El transporte principal transporta datos de imagen de 16 bits a través de un único flujo en serie de alta velocidad junto con un transporte de canal de control bidireccional de baja latencia compatible con I2C. La carga útil de 16 bits incluye opciones de integridad de datos seleccionables de CRC (comprobación de redundancia cíclica) o bits de paridad para controlar los errores del enlace de transmisión. La tecnología de reloj integrada de National permite una comunicación full-duplex transparente sobre un solo par diferencial, lo que permite que la información de control bidireccional asimétrica se transmita independientemente del intervalo de borrado de video. Este flujo serial único elimina los problemas de desviación entre las rutas de datos paralelas y las rutas de reloj, lo que simplifica la transferencia de buses de datos anchos a través de pistas y cables de PCB. Esto reduce las rutas de datos, reduce las capas de PCB, el ancho del cable, el tamaño del conector y los pines, lo que genera un ahorro significativo en los costos del sistema.

Además, la entrada del deserializador proporciona control de ecualización para compensar las pérdidas de los medios en largas distancias. La codificación/descodificación balanceada de CC interna se utiliza para admitir interconexiones acopladas de CA.

La función de suspensión proporciona modos de ahorro de energía e interrupciones de activación remota para señalar dispositivos remotos.

El serializador viene en un paquete LLP de 32 pines y el deserializador viene en un paquete LLP de 40 pines.

característica

- Rendimiento de datos configurable

- 12 bits (minutos) hasta 600 Mbps

- 16 bits (predeterminado) hasta 800 Mbit/s

- 18 bits (máximo) Hasta 900 Mbit/s

- Admite relojes de entrada de 10 MHz a 50 MHz

- Reloj integrado con codificación balanceada de CC para admitir interconexiones acopladas a CA

- Capaz de conducir hasta 10 metros de par trenzado blindado

- Canal de interfaz de control bidireccional con soporte I2C

- Interfaz I2C para configuración de dispositivos.Direccionamiento de ID de pin único

- Carga útil de datos de 16 bits con CRC (verificación de redundancia cíclica) para verificar la integridad de los datos con detección de errores de transmisión de datos programable y control de interrupciones

- Hasta 6 GPIO programables

- Diagnóstico AT-SPEED BIST para verificar la integridad del enlace

- Control de apagado separado para SER y DES

- Borde de reloj de datos paralelo seleccionable por el usuario para SER y DES

- Resistencia de terminación integrada

- Interfaz de bus paralelo compatible con 1,8 V o 3,3 V

- Fuente de alimentación única de 1,8 V

- Cumple con IEC 61000–4–2 ESD

- El deserializador no requiere un reloj de referencia

- Ecualización de recepción programable

- PIN de informe de salida LOCK para verificar el estado del enlace

- Mitigación de EMI/EMC

- Salida de espectro ensanchado programable (SSCG) DES

- Salida escalonada del receptor DES

- Rango de temperatura -40°C a +85°C

- Paquete SER: LLP de 32 pines (5 mm x 5 mm)

- Paquete DES: LLP de 40 pines (6 mm x 6 mm)