Xilinx está anunciando dos importantes avances en productividad como parte de un nuevo lanzamiento importante de Vivado™ Design Suite, la primera suite de diseño programable SoC de la industria. La versión 2013.1 de Vivado Design Suite incluye un nuevo entorno de diseño centrado en IP para una integración más rápida del sistema y un conjunto completo de bibliotecas para acelerar el diseño a nivel de sistema C/C++ y la síntesis de alto nivel (HLS).Xilinx está anunciando dos importantes avances en productividad como parte de un nuevo lanzamiento importante de Vivado™ Design Suite, la primera suite de diseño programable SoC de la industria. La versión 2013.1 de Vivado Design Suite incluye un nuevo entorno de diseño centrado en IP para una integración más rápida del sistema y un conjunto completo de bibliotecas para acelerar el diseño a nivel de sistema C/C++ y la síntesis de alto nivel (HLS).

*Tiempo reducido para crear e integrar IP*

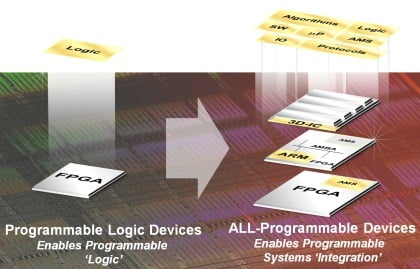

Para facilitar la creación de diseños complejos y altamente integrados en todos los dispositivos FPGA programables, Xilinx ha proporcionado una versión de acceso anticipado de Vivado IP Integrator (IPI). Vivado IPI acelera la integración de RTL, Xilinx IP, IP de terceros e IP de síntesis C/C++. Vivado IPI proporciona ensamblaje inteligente correcto por construcción de diseños co-optimizados con soluciones totalmente programables de Xilinx basadas en estándares de la industria como la interconexión ARM® AXI y los metadatos IP-XACT para empaquetar IP. Construido sobre la base de Vivado Design Suite, IP Integrator proporciona interconexión AXI automática con reconocimiento de IP, generación de subsistemas IP con un solo clic, DRC en tiempo real, propagación de cambios de interfaz y potentes capacidades de depuración. Al enfocarse en el SoC totalmente programable Zynq™-7000, los equipos de diseño integrado pueden identificar, reutilizar e integrar más rápidamente tanto el software como el hardware. IP apuntando a sistemas de procesamiento ARM de doble núcleo y estructuras FPGA de alto rendimiento. Ahora es posible.

dijo Shep Siegel, CTO de Atomic Rules LLC. “La combinación de Vivado IPI con el silicio de la serie 7 acelera nuestro cronograma de desarrollo. Lo he hecho”.

Mire este video para ver una demostración de Vivado IP Integrator.

*Bibliotecas para acelerar el diseño a nivel de sistema*

Para acelerar el diseño a nivel de sistema C/C++ y la síntesis de alto nivel (HLS), Xilinx ha mejorado la biblioteca Vivado HLS para admitir capacidades de procesamiento de video en tiempo real y matemáticas de coma flotante estándar de la industria. Más de 350 usuarios activos y más de 1000 clientes que evalúan Vivado HLS ahora tienen acceso inmediato a capacidades de procesamiento de video integradas en el entorno OpenCV para visión integrada que se ejecuta en sistemas de procesamiento ARM de doble núcleo. La solución resultante puede mejorar el rendimiento de los algoritmos C/C++ existentes hasta 100 veces mediante la aceleración de hardware. Al mismo tiempo, Vivado HLS acelera la verificación del sistema y los tiempos de implementación hasta 100 veces en comparación con los flujos de entrada de diseño RTL. Al apuntar al SoC totalmente programable Zynq-7000, los equipos de diseño ahora pueden desarrollar código C/C++ más rápidamente para sistemas de procesamiento ARM de doble núcleo, con funciones de computación intensiva habilitadas automáticamente en la estructura FPGA de alto rendimiento.

Para obtener más información sobre cómo Xilinx está una generación por delante con Vivado Design Suite, visite www.xilinx.com/vivado.

*disponibilidad*

Descargue Vivado Design Suite 2013.1 ahora desde www.xilinx.com/download. Para obtener acceso anticipado al nuevo soporte de Vivado Design Suite para el integrador de IP y el SoC completamente programable Zynq-7000, comuníquese con su equipo de ventas local. Regístrese o vea la capacitación en línea de Vivado Design Suite y aproveche los diseños de referencia específicos basados en Vivado Design Suite para aumentar su productividad.