Synopsys anunció hoy el lanzamiento 2010.12 de su plataforma de implementación Galaxy™, que ofrece nueva tecnología para abordar las necesidades de escalabilidad, convergencia y rendimiento de los diseños de “gigaescala”.

Synopsys anunció hoy el lanzamiento 2010.12 de su plataforma de implementación Galaxy™, que ofrece nueva tecnología para abordar las necesidades de escalabilidad, convergencia y rendimiento de los diseños de “gigaescala”. Los equipos de ingeniería pueden aprovechar los beneficios de productividad de los diseños de circuitos integrados (IC) grandes y complejos con un rendimiento de tiempo de ejecución más rápido gracias al procesamiento multinúcleo y las innovaciones que mejoran las capacidades de diseño en toda la plataforma Galaxy. Además, la plataforma Galaxy incluye soporte completo de nodo de proceso de silicio de 28 nanómetros (nm) validado por fundición para todas las reglas de verificación de reglas de enrutamiento y diseño (DRC), requisitos de extracción y litografía. La versión Galaxy 2010.12 ya está disponible.

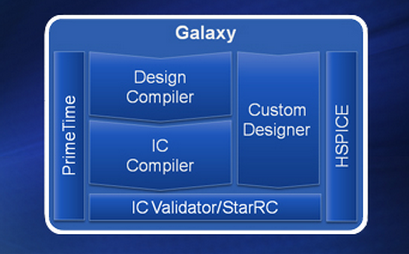

La creciente demanda de productos electrónicos de consumo, como teléfonos inteligentes, tabletas multimedia y televisores de alta definición conectados a Internet, está impulsando a las empresas de semiconductores a implementar rápidamente diseños de circuitos integrados de gigaescala de varios millones de instancias e integrados de forma masiva. Al unir la síntesis lógica, la implementación física y la aprobación en una plataforma integrada, la plataforma Galaxy de Synopsys ofrece la escalabilidad y el rendimiento esenciales para implementar los circuitos integrados más grandes diseñados para tecnologías de procesos de vanguardia. Los componentes clave de la plataforma Galaxy incluyen:

- Design Compiler® Graphical con IC Compiler: desde la exploración del diseño inicial hasta la optimización y temporización simultánea de múltiples esquinas/multimodo (MCMM), potencia, capacidad de prueba y cierre de área, proporcionando una convergencia más rápida de RTL a físico.

- Tecnología Zroute de IC Compiler: proporciona enrutamiento de diseño para la fabricación (DFM) para tecnologías de proceso avanzadas. Combinado con la verificación física In-Design con IC Validator, permite el enrutamiento listo para litografía de múltiples núcleos más rápido y el cumplimiento total de las complejas reglas de DRC requeridas para los nodos de silicio avanzados.y

- Tecnología PrimeTime® HyperScale: Acelera el cierre de tiempo a nivel de bloque en el contexto de diseños de nivel superior, acelerando drásticamente la aprobación de diseños jerárquicos complejos.

Entre las mejoras tecnológicas principales, la versión Galaxy 2010.12 ofrece mejoras significativas en el tiempo de ejecución y la capacidad, que incluyen:

- Síntesis RTL

- Reducción promedio del 25 % en la holgura de sincronización negativa total en DC Ultra™ para un cierre de diseño más predecible

- implementación física

- La tecnología mejorada de carga bajo demanda (ODL) en IC Compiler acelera la finalización del diseño físico de nivel superior en 2-3 veces

- Reparación automática DRC In-Design 7 veces más rápida

- cerrar sesión

20% mejor tiempo de ejecución y memoria para PrimeTime- Una nueva función en PrimeTime que admite el análisis de malla de reloj con precisión SPICE. Tecnología esencial requerida para diseños que incorporan núcleos de procesador.

- Las mejoras de la tecnología PrimeTime HyperScale mejoran la eficiencia del tiempo de ejecución para diseños con bloques de instancias múltiples

- Extracción de parásitos 1,5x (1,5x) más rápida con StarRC™

- De RTL a GDSII

- La creación de nuevos árboles de búfer y las técnicas agresivas de recuperación de área reducen las celdas de búfer e inversor en un promedio del 10 %, lo que mejora la potencia, la capacidad de ruta y el área.

“Los dispositivos SoC de gigaescala de próxima generación requieren soluciones de implementación de alto rendimiento con capacidad de varios millones de instancias y convergencia rápida para completar el diseño”, dijo Antun Domic, vicepresidente senior y gerente general del Grupo de Implementación de Synopsys. “La versión 2010.12 de nuestra plataforma Galaxy brinda a los diseñadores una solución integral para sus necesidades avanzadas, incluido el soporte para tecnología de proceso de vanguardia de 28 nanómetros”.