El LMK04828 es parte de la familia LMK04820 de TI de los acondicionadores de reloj compatibles con JEDEC JESD204B de mayor rendimiento de la industria. El dispositivo integra características de ruido ultrabajo y un PLL de doble bucle.

El LMK04828 es parte de la familia LMK04820 de TI de los acondicionadores de reloj compatibles con JEDEC JESD204B de mayor rendimiento de la industria. El dispositivo integra características de ruido ultrabajo y un PLL de doble bucle.

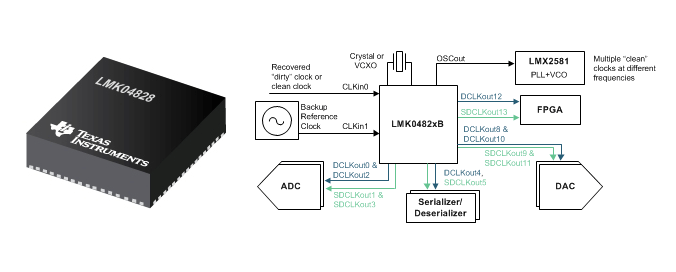

Las 14 salidas de reloj de PLL2 se pueden configurar para controlar 7 convertidores JESD204B u otros dispositivos lógicos utilizando relojes de dispositivos y relojes SYSREF. SYSREF se puede proporcionar utilizando acoplamiento de CC y CA. Sin limitarse a las aplicaciones JESD204B, cada una de las 14 salidas se puede configurar individualmente como salidas de alto rendimiento para sistemas de reloj convencionales.

La familia LMK04820 es ideal para proporcionar árboles de reloj flexibles de alto rendimiento debido a su alto rendimiento combinado con características como compensaciones de rendimiento de potencia, VCO duales, retraso digital dinámico, retención y retraso analógico sin fallas.

característica

- Soporte JEDEC JESD204B

- Jitter y rendimiento RMS ultrabajos

– Jitter de 88 fs RMS (12 kHz a 20 MHz)

– Jitter de 91 fs RMS (100 Hz a 20 MHz)

– –162,5 dBc/Hz de ruido de fondo a 245,76 MHz - Hasta 14 relojes de dispositivos diferenciales de PLL2

– Hasta 7 relojes SYSREF

– Frecuencia máxima de salida del reloj 3,1 GHz

– Salidas programables LVPECL, LVDS, HSDS, LCPECL desde PLL2 - Hasta 1 salida VCXO/cristal almacenada en búfer desde PLL1

– LVPECL, LVDS, 2xLVCMOS programables - Arquitectura PLL de bucle doble PLLatinum

- PLL1

– Hasta 3 relojes de entrada redundantes

– Modos de conmutación automática y manual

– Conmutación sin impacto y LOS

– Circuito oscilador de cristal de bajo ruido integrado

– Modo de espera cuando se pierde el reloj de entrada - PLL2

– Normalizado [1 Hz] Nivel de ruido PLL -227 dBc/Hz

– Tasa de detección de fase hasta 155 MHz

– Multiplicador de frecuencia OSCin

– Dos VCO integrados de bajo ruido - División de salida del ciclo de trabajo del 50%, 1 a 32 (par e impar)

- Retardo digital de precisión, dinámicamente ajustable

- Retardo analógico de paso de 25 ps

- Multimodo: distribución de reloj con PLL dual, PLL simple y 0 opciones de retardo

- Rango de temperatura industrial: –40 a 85°C

- Funcionamiento de 3,15 V a 3,45 V

- Paquete: QFN de 64 pines (9,0 x 9,0 x 0,8 mm)