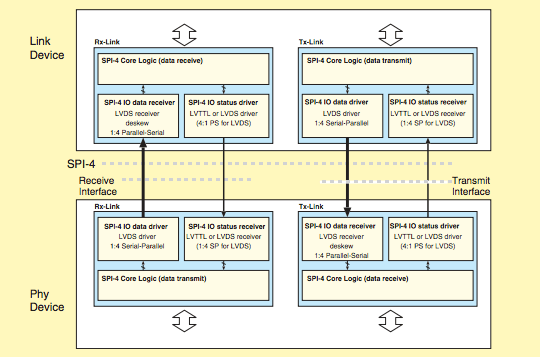

El núcleo de interfaz SPI-4 permite la interconexión de dispositivos de capa física para vincular dispositivos de capa para aplicaciones POS, ATM y Ethernet de 10 Gb/s. La interfaz SPI-4 utiliza búferes de E/S LVDS combinados con registros de doble velocidad de datos (DDR) dedicados en la ruta de datos y búferes de E/S LVTTL en la ruta de estado FIFO. La tasa de datos internos se reduce al extender la palabra de 16 bits en formato DDR en la interfaz SPI-4 a un formato de reloj de un solo borde de 64 bits (4 palabras) que se ejecuta a la mitad de la tasa de reloj de la interfaz SPI-4.El núcleo de interfaz SPI-4 permite la interconexión de dispositivos de capa física para vincular dispositivos de capa para aplicaciones POS, ATM y Ethernet de 10 Gb/s. La interfaz SPI-4 utiliza búferes de E/S LVDS combinados con registros de doble velocidad de datos (DDR) dedicados en la ruta de datos y búferes de E/S LVTTL en la ruta de estado FIFO. La tasa de datos internos se reduce al extender la palabra de 16 bits en formato DDR en la interfaz SPI-4 a un formato de reloj de un solo borde de 64 bits (4 palabras) que se ejecuta a la mitad de la tasa de reloj de la interfaz SPI-4.

*característica*

* Conexión punto a punto entre un solo PHY y un dispositivo de capa de enlace único

* Cumple con el estándar OIF SPI4-02.0 System Packet Interface Level 4 (SPI-4) Phase 2

* Admite ancho de banda agregado para OC192, Ethernet de 10 Gb/s y aplicaciones PoS

* Paquete sobre SONET (POS) PHY Nivel 4 con FIFO

* Admite MUX/DEMUX y función de puente

* Ruta de transmisión/recepción de datos de 16 bits de ancho

* Transmitir/recibir interfaz de estado FIFO a través de LVTTL o LVDS I/O

* La macro del receptor de datos IO SPI-4 consiste en un receptor LVDS (16 datos + 1 control + 1 reloj), corrección de bits secundarios y DEMUX 1:4.

* El SPI-4 IO Data Driver Macro consta de controladores LVDS (16 datos + 1 control + 1 reloj) y un MUX 4:1.

* La macro del receptor de estado SPI-4 IO consiste en un receptor LVDS (estado FIFO de 2 bits + 1 reloj), alineamiento de subbits y DEMUX 1:4.

* La macro del controlador de datos de estado SPI-4 IO consiste en un controlador LVDS (estado FIFO de 2 bits + 1 reloj) y 4:1 MUX.