El SoC de infraestructura de comunicaciones TMS320TCI6618 es miembro de la familia de dispositivos KeyStone. Se basa en la arquitectura SoC multinúcleo KeyStone de TI que utiliza el núcleo C66x DSP. Diseñado específicamente para operaciones 2G, 3G y 4G multiestándar, el TCI6618 duplica el rendimiento de LTE de las soluciones anteriores al tiempo que reduce el consumo de energía SoC a 0,075 mW/potencia GMAC para estaciones base macro y compactas.

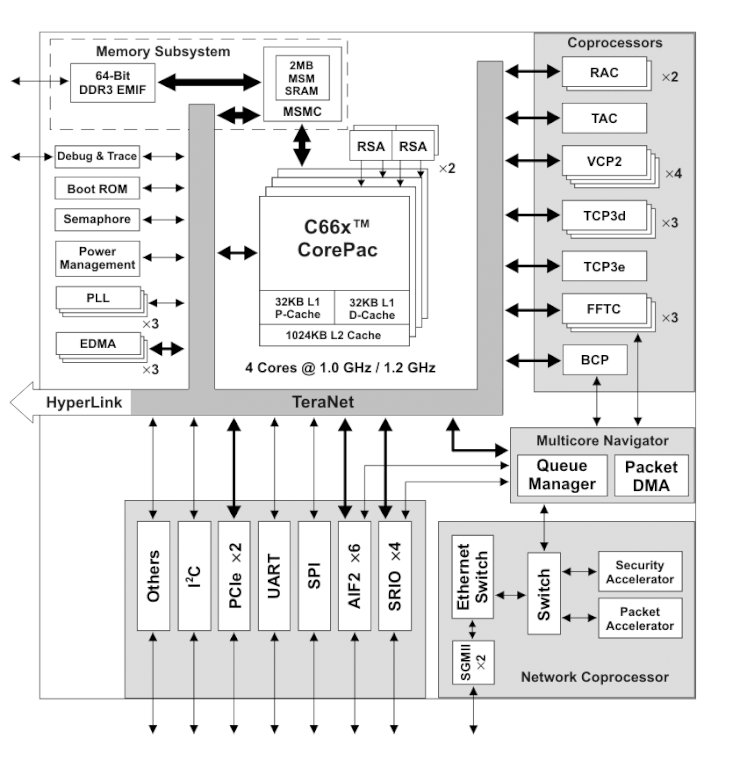

El SoC de infraestructura de comunicaciones TMS320TCI6618 es miembro de la familia de dispositivos KeyStone. Se basa en la arquitectura SoC multinúcleo KeyStone de TI que utiliza el núcleo C66x DSP. Diseñado específicamente para operaciones 2G, 3G y 4G multiestándar, el TCI6618 duplica el rendimiento de LTE de las soluciones anteriores al tiempo que reduce el consumo de energía SoC a 0,075 mW/potencia GMAC para estaciones base macro y compactas. Basada en tecnología de proceso de 40 nm, la plataforma de estación base macro TCI6618 proporciona potencia de procesamiento DSP de 4,8 GHz y admite estándares inalámbricos como WCDMA/HSPA/HSPA+, TD-SCDMA, GSM, TDD – LTE, FDD – LTE y WiMAX.

característica

- Cuatro paquetes de núcleo TMS320C66x DSP a 1,2 GHz

- 153,6 GMAC/76,8 GFLOP a 1,2 GHz

- 32 KB L1P, 32 KB L1D, 1024 KB L2 por núcleo

- L2 compartido de 2 MB

- Multicore Navigator y TeraNet Switch Fabric – 2 Tb

- Coprocesador de red con acelerador de paquetes y acelerador de seguridad

- SRIO 2.1 con 4 carriles: dúplex completo de 5 Gbaudios por carril

- PCIe Gen2 de 2 carriles: dúplex completo de 5 Gbaud por carril

- HyperLink: operación de 50 Gbaudios, dúplex completo

- Subsistema Ethernet MAC: 2 puertos SGMII para operación de 10/100/1000 Mbps

- Interfaz DDR3 de 4 bits (DDR3-1333): 8 GB de espacio de memoria direccionable

- Interfaz de antena basada en SerDes de 6 carriles (AIF2): funciona hasta 6,144 Gbps

- coprocesador de hardware

- coprocesador de tasa de bits

- Coprocesador mejorado para codificación turbo

- 3 coprocesadores mejorados para decodificación turbo

- 4 decodificadores Viterbi

- 3 coprocesadores de transformada rápida de Fourier

- Dos aceleradores de recepción WCDMA y un acelerador de transmisión WCDMA

- Cuatro aceleradores Rake Search para procesamiento de tasa de chip y decodificación Reed-Muller