MoSys ha anunciado un nuevo Bandwidth Engine ® IC de segunda generación optimizado para un alto rendimiento de acceso aleatorio en aplicaciones de red de 100G, 200G y 400G. El dispositivo se basa en una arquitectura de partición de banco único y puerto dual que reduce drásticamente los tiempos de ciclo de acceso aleatorio, lo que permite aumentos dramáticos en las capacidades de velocidad de procesamiento de los equipos de red. La familia de circuitos integrados Bandwidth Engine está diseñada y construida para aplicaciones de nivel portador de alta confiabilidad.

MoSys ha anunciado un nuevo Bandwidth Engine ® IC de segunda generación optimizado para un alto rendimiento de acceso aleatorio en aplicaciones de red de 100G, 200G y 400G. El dispositivo se basa en una arquitectura de partición de banco único y puerto dual que reduce drásticamente los tiempos de ciclo de acceso aleatorio, lo que permite aumentos dramáticos en las capacidades de velocidad de procesamiento de los equipos de red. La familia de circuitos integrados Bandwidth Engine está diseñada y construida para aplicaciones de nivel portador de alta confiabilidad.

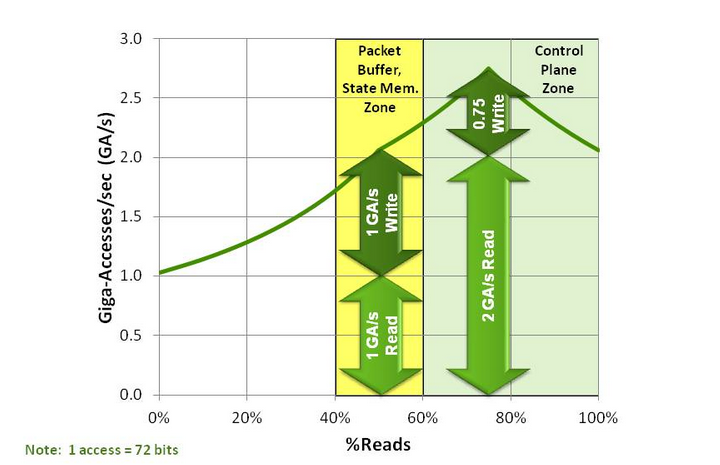

Un nuevo dispositivo, el MSR720, amplía las capacidades del motor de ancho de banda con la capacidad de leer y escribir en ubicaciones de memoria específicas simultáneamente. Una arquitectura de dispositivo única mantiene la coherencia total de los datos, la alta eficiencia de comando y la programación simplificada, lo que brinda accesos de hasta 4,5 giga por segundo (GA/s). La alta tasa de acceso y el tiempo de ciclo efectivo reducido del dispositivo de acceso MSR720 se adaptan bien a los requisitos de la memoria de estado y las aplicaciones de cola que requieren accesos repetidos a la misma dirección.

Usando 16 carriles SerDes a 15 Gigabits por segundo (Gbps), la interfaz MSR720 opera a 480 Gbps, brindando a los hosts un rendimiento de datos efectivo de hasta 270 Gbps con protección CRC. El dispositivo también admite una capacidad de escritura de media palabra de 36 bits que mejora la utilización del bus de comandos. La culminación de estas funciones aumenta el rendimiento más allá de las capacidades de los subsistemas de memoria estándar al tiempo que reduce el espacio de la placa, la cantidad de pines de interfaz utilizados y el consumo de energía.

Los requisitos de tasa de acceso para los sistemas de red superan con creces los que permiten el acceso en tiempo real a los datos del encabezado del paquete con soluciones tradicionales. La arquitectura Bandwidth Engine de segunda generación llena esta brecha de rendimiento para los clientes con la arquitectura del dispositivo MSR720, cumple con estos requisitos y ofrece la solución de memoria de red de un solo chip de mayor rendimiento disponible en la actualidad.

“Nuestra arquitectura de motor de ancho de banda de segunda generación admite variantes especializadas para optimizar aplicaciones y tipos de acceso específicos”, dijo John Monson. “La adición de la verdadera capacidad de acceso aleatorio y el tiempo de ciclo efectivo reducido al MSR720 permite un rendimiento de vanguardia para aplicaciones de red de alta velocidad de datos y baja latencia, como memoria de estado, colas y programación”.

La familia de circuitos integrados Bandwidth Engine de MoSys utiliza la interfaz GigaChip™, un protocolo de transporte abierto, confiable y con un 90 % de eficiencia optimizado para la comunicación de chip a chip. El dispositivo es compatible con CEI-11G y XFI SerDes, lo que permite una interfaz perfecta con bibliotecas estándar disponibles de proveedores de FPGA y ASIC de alto rendimiento. Un paquete completo de RTL y herramientas está disponible para admitir la interfaz del motor de ancho de banda.

Los circuitos integrados de motor de ancho de banda de primera generación de MoSys están totalmente calificados para aplicaciones de nivel de operador y están disponibles para producción en volumen ahora. Para conocer los precios y la disponibilidad de Bandwidth Engine, comuníquese con su representante de ventas local de MoSys en http://www.mosys.com/contact.php.