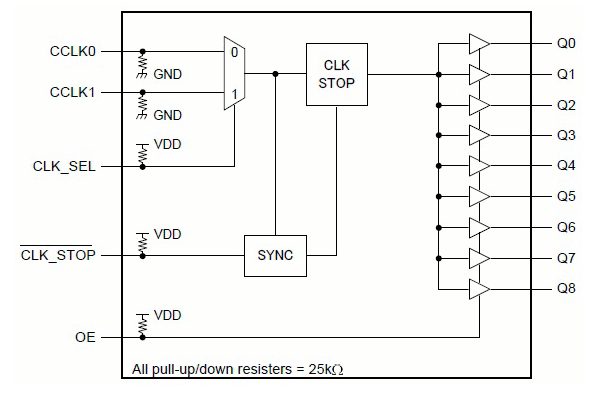

Presentamos la familia AK8180x, un nuevo conjunto de búferes de salida de reloj LVCMOS para aplicaciones informáticas y de comunicaciones. El control de parada del reloj está sincronizado con el flanco descendente del reloj de entrada. Elimine los posibles pulsos cortos de salida al permitir que la señal del reloj de salida comience y se detenga solo en el estado lógico bajo. La aplicación del control de habilitación de salida fuerza la salida a un modo de alta impedancia. Todos los dispositivos funcionan a 3,3 V o 2,5 V. Fabricado con el proceso CMOS de AKM, este nuevo conjunto familiar ofrece alto rendimiento a bajo costo y está alojado en un paquete LQFP de 32 pines.El AK8180B tiene 2 entradas LVCMOS seleccionables por pin y 9 búferes de salida LVCMOS. Funciona con una entrada de reloj de hasta 350MHz y tiene un sesgo de salida a salida de 150ps. AK8180B es totalmente compatible con IDT MPC9447.

El AK8180C tiene 2 entradas LVCMOS o LVPECL seleccionables por pin y 12 búferes de salida LVCMOS. Funciona con una entrada de reloj de hasta 350MHz y tiene un sesgo de salida a salida de 150ps. AK8180C es totalmente compatible con IDT MPC9448. El AK8180 B y C tienen un control de parada de reloj sincronizado con el flanco descendente del reloj de entrada. Esto permite que la señal del reloj de salida comience y se detenga solo en el estado lógico bajo, lo que elimina los posibles pulsos cortos de salida. La aplicación del control de habilitación de salida fuerza la salida a un modo de alta impedancia.

El AK8180D tiene entradas LVPECL diferenciales y 10 búferes de salida LVCMOS. Funciona con una entrada de reloj de hasta 250MHz y tiene un sesgo de salida a salida de 200ps. Los búferes de salida están organizados en tres bancos numerados 3 – 3 – 4, cada uno con controles de habilitación y divisores independientes. AK8180D es totalmente compatible con IDT MPC9456.