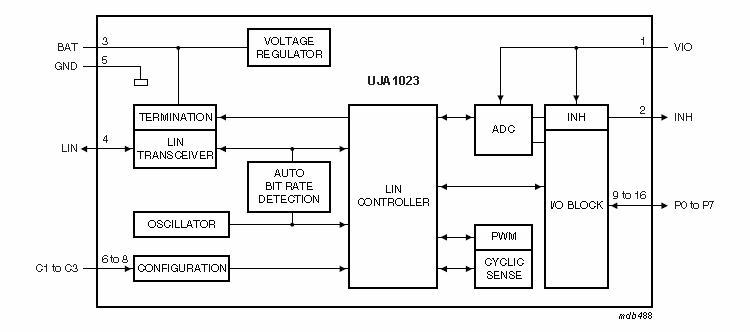

El UJA1023 es un esclavo de E/S independiente de red de interconexión local (LIN) que reemplaza los componentes básicos comúnmente utilizados en las unidades de control electrónico para el procesamiento de entrada/salida. El UJA1023 incluye un controlador LIN 2.0, un transceptor LIN integrado compatible con LIN 2.0/SAE J2602 y LIN 1.3, una resistencia de terminación de 30 kΩ necesaria para esclavos LIN y 8 puertos de E/S configurables a través del bus LIN.

El circuito de sincronización automática de tasa de bits se adapta a cualquier tasa de bits (maestra) entre 1 kbit/sy 20 kbit/s. Se incluye un oscilador para este propósito.

El protocolo LIN se maneja de forma autónoma y la programación tanto de la dirección de nodo (NAD) como del identificador de trama (ID) de LIN se realiza mediante la solicitud del maestro y los mensajes de respuesta del esclavo opcionales combinados con capacidades de codificación en cadena o enchufe.

Los ocho pines de E/S bidireccionales se pueden configurar a través de mensajes de bus LIN y pueden tener las siguientes funciones:

*aporte:*

*Terminal de entrada estándar

* despertar local

* Captura de borde en borde descendente, borde ascendente o ambos bordes

*Terminal de entrada analógica

* Matriz de conmutación (combinación con terminales de salida)

*producción:*

* Pin de salida estándar como controlador de lado alto, controlador de lado bajo o controlador push-pull

* Modo de sentido cíclico para despertar local

* Modo PWM, por ejemplo, para iluminación de fondo

* Matriz de conmutación (combinación con terminales de entrada)

Al ingresar al modo de bajo consumo, se puede mantener el último estado de salida o cambiar a un estado de salida programable por el usuario. En caso de falla (p. ej., bus LIN en cortocircuito a tierra), la salida cambia a un estado de salida de emergencia programable por el usuario y entra en un modo de emergencia de baja potencia.

La operación avanzada de bajo consumo minimiza el consumo de energía de UJA1023 en modo de bajo consumo.

*Características y Beneficios*

* Sincronización automática de tasa de bits a cualquier tasa de bits (maestra) de 1 kbit/s a 20 kbit/s

* Transceptor LIN 2.0 / SAE J2602 integrado (incluye resistencia de terminación de 30 kΩ)

* 8 pines de E/S bidireccionales

* Matriz de interruptores de 4 x 2, 4 x 3 o 4 x 4 que admite lectura y alimentación de hasta 16 interruptores

* Salidas configurables como controladores de lado alto y/o lado bajo y como controladores cíclicos o PWM

* ADC de 8 bits

* Operación avanzada de baja potencia

* Oscilador en chip

* Configuración de dirección de nodo (NAD) por cadena o codificación de enchufe

* Entradas compatibles con activación local y captura de borde

* modo de suspensión configurable

* configuración de limp home en caso de condiciones de error

* Emisiones electromagnéticas extremadamente bajas

* Alta inmunidad a las interferencias electromagnéticas

*Líneas de bus protegidas según ISO 7637

* Rango de temperatura ambiente ampliado (-40 °C a +125 °C)