LeCroy Corporation anunció hoy una nueva plataforma de bajo costo que ofrece bus DDR3 completo y análisis de tiempo JEDEC.

LeCroy Corporation anunció hoy una nueva plataforma de bajo costo que ofrece bus DDR3 completo y análisis de tiempo JEDEC. Kibra™ 380 de LeCroy es el primer analizador de protocolo verdaderamente independiente de la industria para DDR3, que combina una vista de forma de onda y una lista de estados con una lógica de activación dedicada para una mejor visualización de las transiciones de estado DDR3 y las violaciones de protocolo. Diseñado para reducir los costos de prueba para los desarrolladores de sistemas de memoria DDR3, Kibra 380 elimina la necesidad de costosos analizadores lógicos mientras simplifica la configuración y acorta los ciclos de verificación.

“Los mayores obstáculos que enfrentan los equipos de validación cuando comienzan a probar los sistemas de memoria son el costo y la complejidad. Los equipos de diseño de DDR3 de hoy buscan enfoques de prueba que no requieran hardware de preprocesador JEDEC junto con plataformas de análisis lógico de alta gama”, dijo Michael Romm, vicepresidente de desarrollo de productos, Protocol Solutions Group, LeCroy. “El Kibra 380 reemplaza estos sistemas monolíticos con un analizador de bus independiente que incluye todas las capacidades de activación importantes para violaciones de JEDEC mientras captura y muestra formas de onda de tiempo, listas de estados decodificados, rendimiento y estadísticas de utilización”.

Kibra 380 incorpora una vista de forma de onda tradicional y una lista de estados decodificados para un análisis completo del protocolo. La lógica de disparo especial puede identificar simultáneamente más de 65 violaciones de tiempo y comando JEDEC en todos los rangos y bancos. El sistema también aprovecha una gran cantidad de memoria integrada para proporcionar vistas adicionales para ayudar a los desarrolladores a optimizar la utilización de direcciones físicas y la nivelación de carga.

Kibra 380 proporciona captura sin pérdidas de señales de dirección, comando y control (ADD/CMD/CNTRL). Al centrarse en la captura basada en el estado y excluir las señales de datos, el sistema puede registrar más de mil millones de muestras de eventos. Esto es ocho veces la profundidad de memoria que ofrecen las soluciones actuales basadas en analizadores lógicos.

Además del análisis de tiempo, Kibra produce métricas de rendimiento que se muestran para las operaciones de lectura, escritura y apagado. Las métricas de bus se rastrean por banco y por ranura DIMM para brindarle una imagen general de la utilización de la memoria. Se incluye un intercalador DDR3 para alojar módulos de memoria RDIMM y UDIMM. Kibra 380 también es capaz de realizar pruebas DDR3 multicanal mediante analizadores en cascada que utilizan el puerto de sincronización integrado.

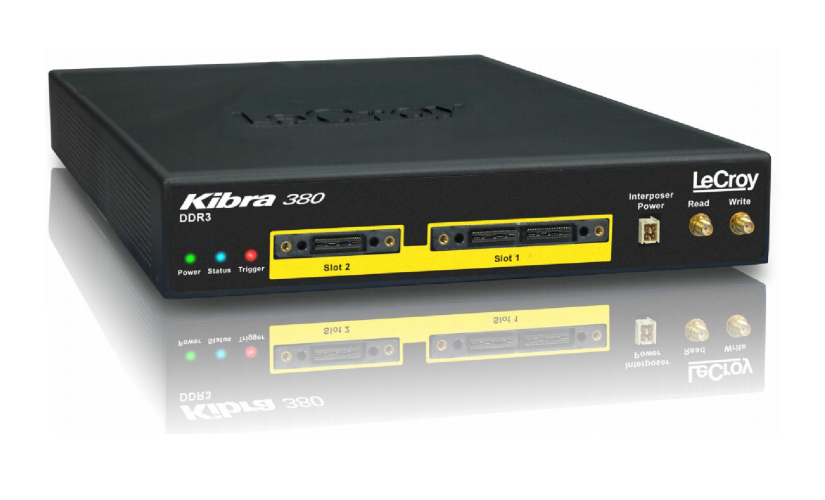

El pequeño y portátil Kibra 380 se puede controlar mediante una PC con Windows e incluye las sondas intercaladoras necesarias capaces de monitorear 2 ranuras de módulos DIMM DDR3 de rango cuádruple que funcionan a 1600 MT/s. Kibra 380 también cuenta con un disparador único en tiempo real para operaciones de lectura/escritura (WE), además de un puerto CrossSync incorporado para realizar análisis multiprotocolo. Esta señal de salida de activación SMA de baja latencia dedicada permite que el osciloscopio realice pruebas de integridad de la señal utilizando la relación DQ/DQS para distinguir las operaciones de lectura/escritura en el bus. El analizador Kibra 380 estará disponible en el segundo trimestre de 2011.