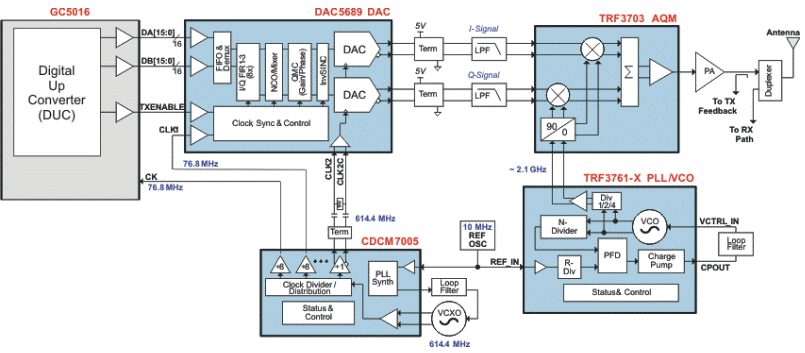

El DAC5689 es un convertidor de digital a analógico (DAC) de dos canales, 16 bits y 800 MSPS. , compensación IQ y voltaje de referencia interno. Diferentes modos de operación habilitan o evitan varios bloques de procesamiento de señales. El DAC5689 ofrece un excelente rendimiento de linealidad, ruido y diafonía.

El DAC5689 es un convertidor de digital a analógico (DAC) de dos canales, 16 bits y 800 MSPS. , compensación IQ y voltaje de referencia interno. Diferentes modos de operación habilitan o evitan varios bloques de procesamiento de señales. El DAC5689 ofrece un excelente rendimiento de linealidad, ruido y diafonía.

El bus de datos CMOS dual DAC5689 proporciona una transferencia de datos de entrada de 250 MSPS por canal DAC. Varias opciones de datos de entrada están disponibles. FIFO de entrada con datos de bus doble, datos intercalados de bus único, multiplexación par e impar a mitad de velocidad y un reloj externo o interno para facilitar la temporización de la interfaz. Los datos de entrada se pueden interpolar a 2x, 4x u 8x mediante un filtro FIR de interpolación digital integrado con una atenuación de banda suprimida superior a 80 dB.

El DAC5689 permite salidas tanto complejas como reales. Un NCO/mezclador de 32 bits de modo combinado opcional proporciona conversión ascendente de frecuencia y las salidas DAC duales producen un par de transformadas Hilbert combinadas. Un filtro de sinc inverso digital compensa la atenuación de frecuencia sin(x)/x natural del DAC. La función de corrección de modulador de cuadratura digital (QMC) permite la compensación de IQ para fase, ganancia y compensación para maximizar el rechazo de banda lateral para moduladores de cuadratura externos que realizan conversión ascendente de RF de banda lateral única final, se puede minimizar la alimentación directa de LO.

El DAC5689 es pin actualizable al DAC5688 con PLL de multiplicación de reloj. El DAC5689 funciona en el rango de temperatura industrial de -40 °C a 85 °C y está disponible en un paquete QFN de 64 pines y 9×9 mm.

característica

- DAC doble de 16 bits y 800 MSPS

- Datos de entrada CMOS dobles de 16 bits y 250 MSPS

- FIFO de entrada de 16 muestras

- Opciones de bus de datos de entrada flexibles

- alto rendimiento

- 81 dBc ACLR WCDMA TM1 a 70 MHz

- Filtros de interpolación seleccionables de 2x a 8x

- Atenuación de banda de parada > 80 dB

- Mezclador complejo con NCO de 32 bits

- Corrección del modulador de cuadratura digital

- Corrección de ganancia, fase y compensación

- Filtro SINC Inverso Digital

- Interfaz de control serie de 3 o 4 hilos

- Referencia de 1,2 V en chip

- Salida escalable diferencial: 2-20 mA

- Paquete: 64 pines 9x9mm QFN

solicitud

- estación base de telefonía celular

- Acceso inalámbrico de banda ancha (BWA)

- WiMAX 802.16

- Backhaul inalámbrico fijo

- Sistema de terminación de módem por cable (CMTS)