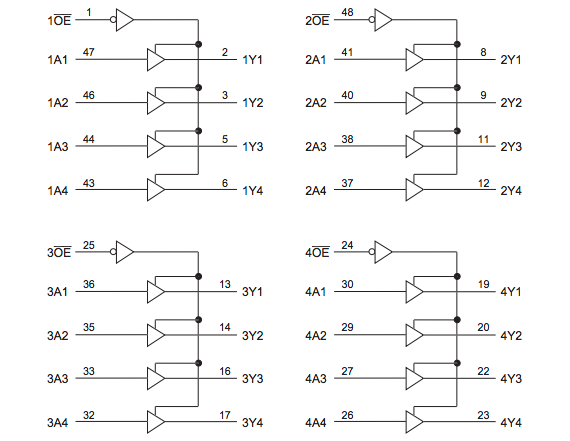

El HD74ALVCH162244 está específicamente diseñado para mejorar tanto el rendimiento como la densidad de los controladores de dirección de memoria de tres estados, controladores de reloj, receptores y transmisores orientados a bus. Este dispositivo se puede utilizar como cuatro búferes de 4 bits, dos búferes de 8 bits o un búfer de 16 bits. Proporciona una entrada de habilitación de salida baja activa (OE) que es simétrica a la salida verdadera.El HD74ALVCH162244 está específicamente diseñado para mejorar tanto el rendimiento como la densidad de los controladores de dirección de memoria de tres estados, controladores de reloj, receptores y transmisores orientados a bus. Este dispositivo se puede utilizar como cuatro búferes de 4 bits, dos búferes de 8 bits o un búfer de 16 bits. Proporciona una entrada de habilitación de salida baja activa (OE) que es simétrica a la salida real.

Para garantizar un estado de alta impedancia durante el encendido o el apagado, el OE debe conectarse a VCC a través de una resistencia pull-up. El valor mínimo de resistencia está determinado por la capacidad de hundimiento actual del controlador. Se proporciona un circuito de retención de bus activo para mantener las entradas de datos flotantes o no utilizadas en un nivel lógico válido. Todas las salidas están diseñadas para absorber hasta 12 mA e incluyen resistencias de 26 Ω para reducir el sobreimpulso y el subimpulso.

*característica*

*Vcc=2.3V a 3.6V

* Rebote de suelo VOL típico 2,0 V (a Vcc = 3,3 V, Ta = 25 °C)

* Alta corriente de salida ±12 mA (a Vcc = 3,0 V)

* La retención de bus en las entradas de datos elimina la necesidad de resistencias pull-up/pull-down externas

* Todas las salidas tienen una resistencia en serie equivalente a 26 Ω, por lo que no se requieren resistencias externas.