El ADC34J45 es un ADC de cuatro canales y 14 bits de 160 MSPS con una interfaz JESD204B. El dispositivo presenta un consumo de energía ultra bajo y una alta linealidad. Este dispositivo está diseñado específicamente para admitir señales de entrada de alta frecuencia exigentes con requisitos de gran rango dinámico. Un divisor de entrada de reloj proporciona flexibilidad en el diseño de la arquitectura del reloj del sistema, y una entrada SYSREF permite la sincronización completa del sistema. El ADC34J45 es compatible con las interfaces Serial Current Mode Logic (CML) y JESD204B para reducir la cantidad de líneas de interfaz, lo que permite una alta densidad de integración del sistema. La interfaz JESD204B es una interfaz en serie y los datos para cada ADC se serializan y emiten a través de un solo par diferencial. Un bucle de bloqueo de fase interno (PLL) multiplica el reloj de muestreo ADC entrante por 20 para derivar los relojes de bits utilizados para serializar los datos de 14 bits de cada canal. El dispositivo ADC34J45 admite la subclase 1 con velocidades de interfaz de hasta 3,2 Gbps.

El ADC34J45 es un ADC de cuatro canales y 14 bits de 160 MSPS con una interfaz JESD204B. El dispositivo presenta un consumo de energía ultra bajo y una alta linealidad. Este dispositivo está diseñado específicamente para admitir señales de entrada de alta frecuencia exigentes con requisitos de gran rango dinámico. Un divisor de entrada de reloj proporciona flexibilidad en el diseño de la arquitectura del reloj del sistema, y una entrada SYSREF permite la sincronización completa del sistema. El ADC34J45 es compatible con las interfaces Serial Current Mode Logic (CML) y JESD204B para reducir la cantidad de líneas de interfaz, lo que permite una alta densidad de integración del sistema. La interfaz JESD204B es una interfaz en serie y los datos para cada ADC se serializan y emiten a través de un solo par diferencial. Un bucle de bloqueo de fase interno (PLL) multiplica el reloj de muestreo ADC entrante por 20 para derivar los relojes de bits utilizados para serializar los datos de 14 bits de cada canal. El dispositivo ADC34J45 admite la subclase 1 con velocidades de interfaz de hasta 3,2 Gbps.

característica

- canal cuádruple

- resolución de 14 bits

- Fuente de alimentación única de 1,8 V

- Búfer de reloj de entrada flexible con división por 1, -2, -4

- SNR = 72dBFS, SFDR = 86dBc (fIN = 70MHz)

- Consumo de energía ultra bajo: 203 mW/Ch a 160 MSPS

- Aislamiento de canal: 105 dB

- interpolación interna

- Interfaz serie JESD204B:

– Soporta subclases 0, 1, 2

– Admite un carril por ADC hasta 160 MSPS - Soporte de sincronización multichip

- Compatible pin a pin con la versión de 12 bits

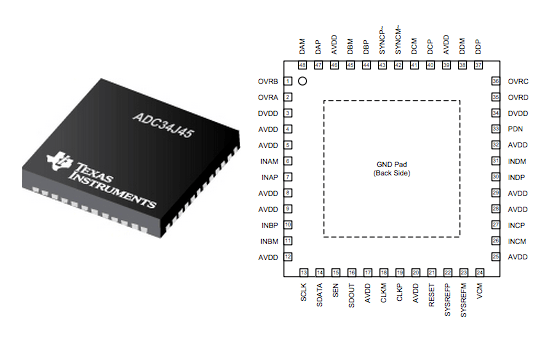

- Paquete: VQFN-48 (7 mm x 7 mm)