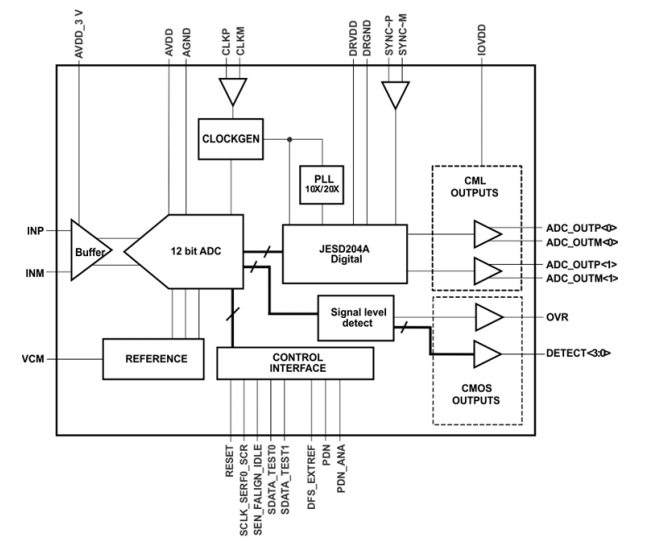

El ADS61JB23 es un convertidor analógico a digital de un solo canal, de bajo consumo y alto rendimiento con una interfaz de salida JESD204A integrada. Disponible en un paquete QFN de 6 mm × 6 mm, el ADS61JB23 presenta modos de salida de un solo carril y de dos carriles para un nivel de compacidad sin precedentes. La interfaz de salida es compatible con el estándar JESD204A y tiene modos adicionales (según IEEE Std 802.3-2002 Part3, cláusula 36.2.4.12) para una conexión perfecta a la familia TI TLK de transceptores SERDES. Igualmente impresionante es la inclusión de un búfer de entrada analógica en el chip. Esto proporciona aislamiento entre los interruptores de muestra/retención y una impedancia de entrada más alta y estable.

El ADS61JB23 es un convertidor analógico a digital de un solo canal, de bajo consumo y alto rendimiento con una interfaz de salida JESD204A integrada. Disponible en un paquete QFN de 6 mm × 6 mm, el ADS61JB23 presenta modos de salida de un solo carril y de dos carriles para un nivel de compacidad sin precedentes. La interfaz de salida es compatible con el estándar JESD204A y tiene modos adicionales (según IEEE Std 802.3-2002 Part3, cláusula 36.2.4.12) para una conexión perfecta a la familia TI TLK de transceptores SERDES. Igualmente impresionante es la inclusión de un búfer de entrada analógica en el chip. Esto proporciona aislamiento entre los interruptores de muestra/retención y una impedancia de entrada más alta y estable.

El ADS61JB23 se especifica en el rango de temperatura industrial (-40 °C a 85 °C).

característica

- Interfaz de salida:

- Interfaz de un solo carril y de dos carriles

- Velocidad máxima de datos 1,6 Gbps

- Cumple con las especificaciones JESD204A

- Salida CML con corriente programable de 2mA a 32mA

- el consumo de energía:

- 440 mW a 80 MSPS en modo de carril único

- La potencia se reduce con la frecuencia del reloj

- Interfaz de entrada: entrada analógica con búfer

- 71,7 dBFS SNR a 70 MHz FI

- Entrada analógica FSR: 2 Vpp

- Soporte para referencias externas e internas (recortadas)

- Suministro de 1,8 V (analógico y digital), suministro de 3,3 V para búferes de entrada

- Ganancia digital programable: 0dB – 6dB

- Salida binaria de compensación directa o complemento a 2

- paquete: