En este tutorial, aprenderemos sobre otro flip-flop importante conocido como T-flip-flop. Conozca el diseño, funcionamiento y algunas aplicaciones de los flip-flops T.

descripción general

Tabla de contenido

introducción

Las chanclas T también se conocen como “chanclas de palanca”. Para evitar la aparición de estados intermedios (también conocidos como estados inhibidos) en un flip-flop SR, solo se debe proporcionar al flip-flop una entrada, llamada entrada de activación o entrada de conmutación (T).

El flip-flop actúa entonces como un interruptor de palanca. Alternar significa “cambiar la salida del siguiente estado para que sea complementaria a la salida del estado actual”.

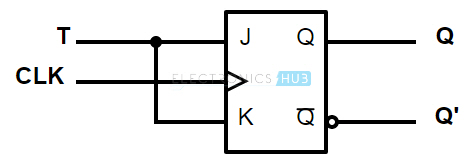

Se puede diseñar un flip-flop T haciendo modificaciones simples al flip-flop JK. Dado que un flip-flop T es un dispositivo de entrada única, puede convertir un flip-flop JK en un flip-flop T conectando las entradas J y K juntas y generando una única entrada llamada T.

Por lo tanto, un flip-flop T a veces se denomina flip-flop JK de entrada única.

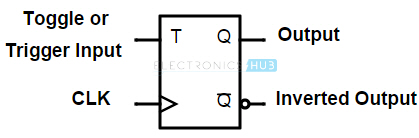

A continuación se muestra el símbolo lógico de un flip-flop T. Hay una entrada de conmutación (T) y una entrada de señal de reloj (CLK).

T-flip – circuito flop

Puedes construir un flip-flop T de una de las siguientes maneras:

- Conecte la retroalimentación de salida a la entrada del flip-flop SR.

- Conecte el XOR con entrada T y salida Q PREVIOUS a la entrada de datos del flip-flop D.

- Duro: conecte las entradas J y K juntas y conéctelas a la entrada T del flip-flop JK.

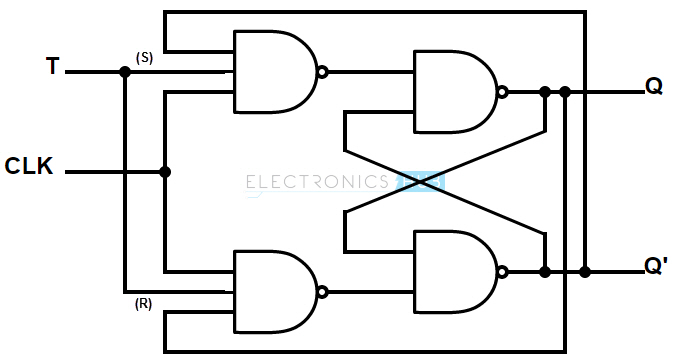

Usando chanclas SR

Se puede construir un flip-flop en T conectando una puerta AND como entrada a un pestillo SR de puerta NOR. Una de las entradas a estas puertas AND es la retroalimentación de la salida del estado actual Q y su complemento. q a cada puerta AND, es decir, Q a la puerta AND asociada con la entrada R, q Conéctese a la puerta AND asociada con la entrada S.

La entrada de palanca (T) se conecta comúnmente como entrada a ambas puertas AND. La puerta AND también está conectada a una señal de reloj común (CLK).

En un flip-flop T, se proporciona un tren de pulsos de disparo estrecho como entrada (T) para provocar un cambio en el estado de salida del flip-flop. Por lo tanto, estas chanclas también se denominan chanclas de palanca. A continuación se muestra el diagrama de circuito de un flip-flop T que consta de un pestillo SR.

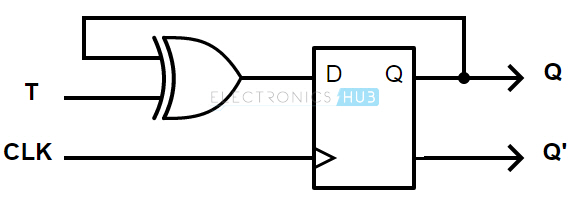

D Usando chanclas

De manera similar, se puede construir un flip-flop T modificando un flip-flop D. En un flip-flop D, la salida Q se aplica en XOR con la entrada T y se alimenta a la entrada D. A continuación se muestra el circuito de un flip-flop T que consta de un flip-flop D.

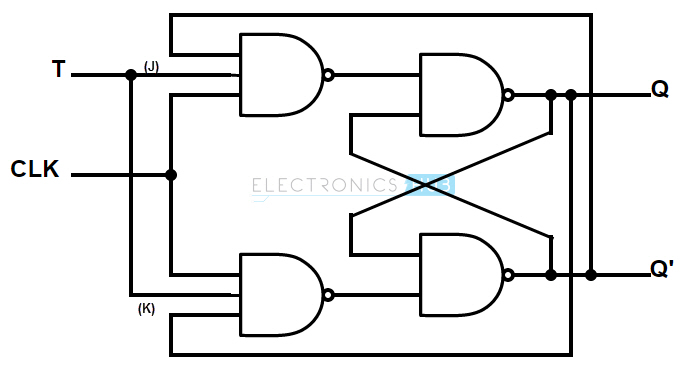

Usando chanclas JK

La estructura de flip-flop T más simple es el flip-flop JK. Las entradas J y K del flip-flop JK están conectadas entre sí y se proporcionan como entrada T. A continuación se muestra el circuito lógico de un flip-flop T que consta de flip-flops JK.

trabajar

Los T-flip-flops son dispositivos activados por flanco. En otras palabras, una transición de bajo a alto o de alto a bajo en la señal del reloj de entrada cambia el estado de salida del flip-flop.

Tabla de verdad del flip-flop T

A continuación se muestra la tabla de verdad para un flip-flop T.

| anterior | Próximo | |||

| t | qAdelante | qAdelante | qPróximo | qPróximo |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 |

Como se mencionó anteriormente, los flip-flops T son dispositivos activados por borde. Por ejemplo, considere un flip-flop T hecho de pestillos NAND SR, como se muestra a continuación.

Cuando la salida Q = 0, la puerta NAND superior (NAND C) está deshabilitada (no hay entrada dominante) y la puerta NAND inferior (NAND D) está habilitada (la retroalimentación de Q es la entrada dominante). Esto significa que la entrada de alternancia establece la condición de entrada. R.S. como una chancla R = 1 y S = 0. Recuerde la siguiente tabla de verdad. R.S. Flip-flop, esta condición establece la salida. Por tanto, Q será 1.

Cuando la salida Q = 1, la NAND superior está habilitada y la puerta NAND inferior está deshabilitada. Esto le permitirá configurar la entrada con alternancia de entrada. R.S. como una chancla R = 0 y S = 1. Esto reinicia el flip-flop, es decir, Q = 0.

Brevemente, un flip-flop T funciona de la siguiente manera.

Si la entrada T es BAJA, el siguiente estado del flip-flop T será el mismo que el estado actual.

- T = 0, estado actual = 0, siguiente estado = 0

- T = 0, estado actual = 1, siguiente estado = 1

Cuando la entrada T es ALTA y la señal del reloj tiene una transición positiva, el siguiente estado del flip-flop T será el complemento del estado actual.

- T = 1, estado actual = 0, siguiente estado = 1

- T = 1, estado actual = 1, siguiente estado = 0

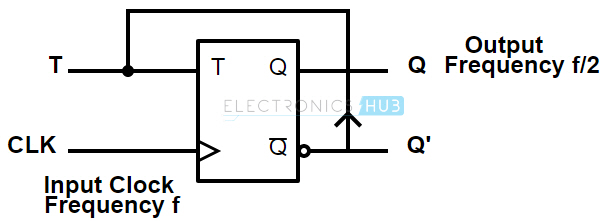

El flip-flop cambia cuando cada disparador de entrada alterna entre las entradas SET y RESET. Por lo tanto, se requieren dos activadores para completar un ciclo completo de la forma de onda de salida. Esto significa que el flip-flop T produce una salida exactamente a la mitad de la frecuencia de la entrada. Por tanto, el flip-flop T actúa como un “divisor de frecuencia”.

El principal inconveniente del flip-flop T es que el estado del flip-flop cuando se aplica el pulso de disparo sólo se conoce si se conoce el estado anterior.

Los flip-flops T generalmente no están disponibles como circuitos integrados. Por lo tanto, se puede construir utilizando flip-flops JK, flip-flops SR y flip-flops D. A continuación se muestra el símbolo de un flip-flop T hecho a partir de un flip-flop JK.

solicitud

Echemos ahora un vistazo a algunas aplicaciones importantes de los flip-flops T.

- Circuito divisor de frecuencia

- 2 – Registro de carga paralela de bits

Circuito divisor de frecuencia

El flip-flop AT se puede utilizar como “circuito divisor” realimentando la salida complementaria Q’ a la entrada T. A continuación se muestra el símbolo lógico de un divisor de frecuencia que utiliza flip-flops T.

Si la frecuencia del reloj de entrada del flip-flop T es ‘f’ Hz, la frecuencia de los pulsos en la salida Q es ‘f/2’ Hz. Muchos de estos circuitos divisores se pueden conectar en cascada para dividir aún más la frecuencia.

Si la frecuencia del reloj de entrada del flip-flop T es ‘f’ Hz, la frecuencia de los pulsos en la salida Q es ‘f/2’ Hz. Muchos de estos circuitos divisores se pueden conectar en cascada para dividir aún más la frecuencia.

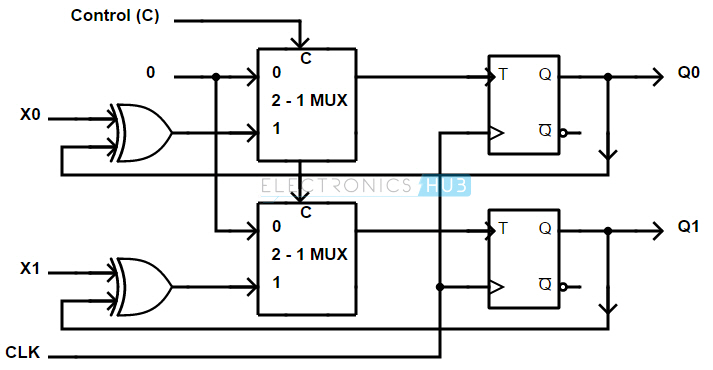

Registro de carga paralelo de 2 bits usando flip-flops T

Utilice registros y registros de desplazamiento para almacenar datos. Sin embargo, el tamaño es siempre la principal preocupación para los elementos de la memoria, como los registros. Por lo tanto, se utiliza un registro de carga paralelo de 2 bits en lugar de un registro de 4 bits.

Se deben considerar dos operaciones al diseñar registros de carga paralelos:

- retener datos

- Cargando datos en paralelo

Para preservar la salida de un flip-flop T, simplemente podemos establecer la entrada T en 0, pero la carga paralela es la parte complicada.

La carga paralela significa obtener el valor X en la salida del flip-flop. Para hacer esto, aplicamos XOR a la entrada X con la salida del estado actual y la alimentamos a un MUX 2 a 1. La otra entrada al MUX es un 0 constante (lógico bajo). La salida del MUX está conectada a la entrada del flip-flop T.

Este es un registro de 2 bits, por lo que se requieren dos combinaciones de este tipo. A continuación se muestra el circuito para un registro de carga paralelo de 2 bits.

conclusión

Un tutorial rápido para principiantes sobre el flip-flop T, también conocido como flip-flop de palanca. Aprendió a diseñar un flip-flop T utilizando otros flip-flop como el flip-flop SR, el flip-flop JK, el flip-flop D, el funcionamiento del flip-flop de palanca, la tabla de verdad del flip-flop T y las parejas. Muchas aplicaciones útiles.

Artículo relacionado:

- SR Flip-Flop – Diseño con puertas y aplicaciones

- 555 Multivibrador astable mediante temporizador | Circuito,…

- Cómo voltear una imagen en Google Docs

- SRAM y DRAM | Comparación, estructura básica y diferencias

- Diferentes tipos de memoria para Arduino | SRAM, EEPROM, Flash

- ¿Cómo configuro los pines GPIO como entradas y salidas en el ESP8266 NodeMCU?