descripción general

Tabla de contenido

- introducción

- cirugía

- Caso 1: Si las entradas J y K son ambas BAJAS, Q devuelve su valor de estado anterior. Es decir, conserva datos anteriores.

- Caso 2: Si J es BAJO y K es ALTO, el flip-flop está en estado de reinicio. Es decir, Q = 0, Q’ = 1.

- Caso 3: Si J es ALTO y K es BAJO, el flip-flop está configurado. Es decir, Q = 1, Q’ = 0

- Caso 4: Si ambas entradas J y K están en ALTO, el flip-flop está en un estado de conmutación. Esto significa que la salida es complementaria al estado anterior.

- mesa de la verdad

- Condiciones de carrera de JK Flip Flop

- Chanclas JK maestro-esclavo

- solicitud

- Artículo relacionado:

introducción

El flip-flop JK lleva el nombre del ingeniero eléctrico Jack Kilby, quien inventó el circuito integrado. Un flip-flop JK se denomina flip-flop programable universal porque sus entradas J, K Preset y Clear se pueden utilizar para imitar la funcionalidad de otros flip-flops.

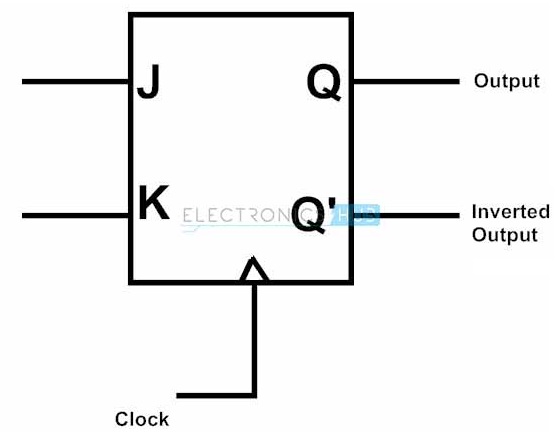

El flip-flop JK es una modificación del flip-flop SR que no tiene estados ilegales. En este caso, la entrada J es similar a la entrada SET de un flip-flop SR, y la entrada K es similar a la entrada RESET de un flip-flop SR. El símbolo del flip-flop JK se muestra a continuación.

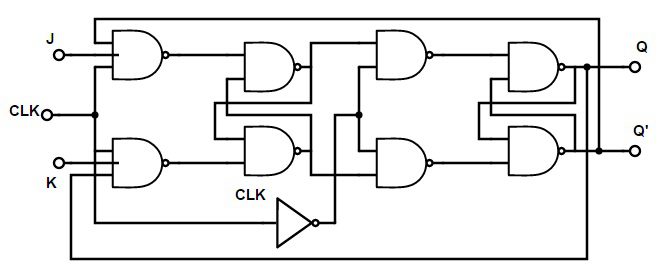

Diagrama lógico del flip-flop JK

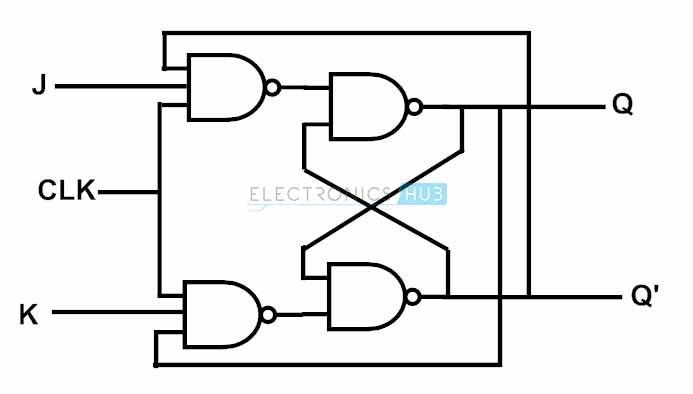

El diagrama lógico del flip-flop JK se muestra en la siguiente figura. Como se mencionó anteriormente, el flip-flop JK es una versión modificada del flip-flop SR. El diagrama lógico se construye reemplazando la puerta NAND de dos entradas del flip-flop SR con una puerta NAND de tres entradas, donde las entradas se reemplazan de S y R a J y K.

En un diseño flip-flop JK, las tres entradas a una puerta NAND son J (la señal de reloj y la señal de retroalimentación de Q’), y las tres entradas a la otra puerta NAND son K (la señal de reloj y la señal de retroalimentación de Q’). ‘).señal de retroalimentación). P. Este mecanismo elimina el estado indefinido del flip-flop SR.

mesa de la verdad

Volver a la cima

cirugía

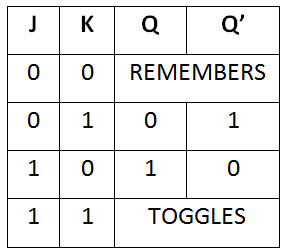

Caso 1: Si las entradas J y K son ambas BAJAS, Q devuelve su valor de estado anterior. Es decir, conserva datos anteriores.

Si aplicamos un pulso de reloj al flip-flop JK y la entrada J es BAJA, la salida de la puerta NAND 1 será ALTA, independientemente de las otras puertas NAND. De manera similar, si la entrada K es baja, la salida de la puerta NAND 2 también será alta. Por tanto, la salida permanece en el mismo estado. Es decir, el estado del flip-flop no cambia.

Caso 2: Si J es BAJO y K es ALTO, el flip-flop está en estado de reinicio. Es decir, Q = 0, Q’ = 1.

Si aplicamos un pulso de reloj al flip-flop JK y las entradas son J baja y K alta, la salida de la puerta NAND conectada a la entrada J será 1. Entonces Q se vuelve 0. Esto restablece el flip-flop nuevamente a su estado anterior. estado. Por lo tanto, el flip-flop está en estado RESET.

Caso 3: Si J es ALTO y K es BAJO, el flip-flop está configurado. Es decir, Q = 1, Q’ = 0

Si aplicamos un pulso de reloj a un flip-flop JK y las entradas son J alta y K baja, la salida de la puerta NAND conectada a la entrada K será 1. Entonces Q’ se vuelve 0. Esto pone el flip-flop en alto. Entrada de reloj. Por lo tanto, el flip-flop está en estado SET.

Caso 4: Si ambas entradas J y K están en ALTO, el flip-flop está en un estado de conmutación. Esto significa que la salida es complementaria al estado anterior.

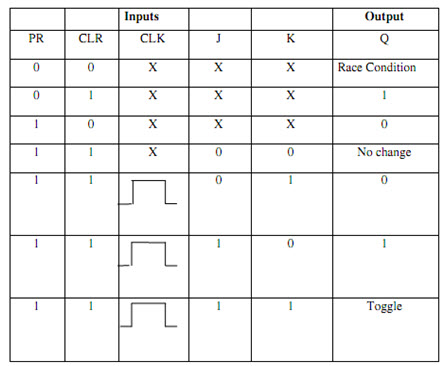

mesa de la verdad

A continuación se muestra la tabla de verdad del flip-flop JK.

Volver a la cima

Condiciones de carrera de JK Flip Flop

Para la entrada alta del flip-flop JK, sólo las puertas NAND inferiores son activadas por sus salidas complementarias, es decir, Q y Q’. Por lo tanto, mientras la entrada alta está conectada al flip-flop, una puerta siempre está habilitada y las otras puertas están deshabilitadas. Cuando la puerta superior está en el estado deshabilitado, el flip-flop pasa al estado SET y, más tarde, cuando la puerta inferior está habilitada, el flip-flop pasa al estado RESET, lo que hace que la salida cambie. Esto provoca una condición de carrera en el flip-flop JK.

Pasos para evitar condiciones de carrera

- Las condiciones de carrera se pueden evitar configurando el tiempo de activación para que sea más corto que el retardo de propagación del flip-flop. Esto se puede lograr con disparadores de borde.

- Cambiando un flip-flop durante un período de reloj. Este concepto se introduce en el flip-flop Master Slave JK.

Volver a la cima

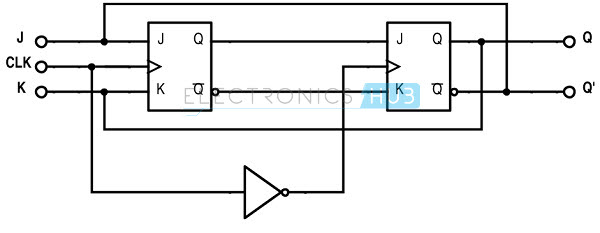

Chanclas JK maestro-esclavo

Los flip-flops JK maestro/esclavo son dispositivos “sincrónicos” que pasan datos en el momento de una señal de reloj. Un flip-flop maestro-esclavo consta de dos flip-flops sincronizados conectados en serie, separando la entrada y la salida, de ahí el término “maestro-esclavo”. Además de eliminar el problema de contención de los flip-flops JK normales, los flip-flops JK maestro-esclavo también pueden imitar la funcionalidad de los flip-flops SR, los flip-flops sincronizados, los flip-flops D y los flip-flops de palanca. Las salidas Q y Q’ del flip-flop esclavo se retroalimentan al flip-flop maestro, y la salida del flip-flop maestro se conecta como una de las entradas del flip-flop esclavo.

Cuando la entrada del reloj es Alta, el maestro está activo y el esclavo está inactivo. Dependiendo de la entrada, la salida del flip-flop maestro se activa o restablece, mientras que la salida del flip-flop esclavo permanece sin cambios y permanece en su estado anterior. Cuando se activa un flip-flop esclavo con una entrada de reloj baja, la salida del flip-flop esclavo cambia. Si el reloj está alto, el esclavo está inactivo durante este período, por lo que la salida del flip-flop maestro se retiene. Cuando el reloj está bajo, la salida del flip-flop maestro es vista por el flip-flop esclavo y pasa a su salida. La salida del flip-flop esclavo es la salida final del flip-flop maestro-esclavo. La salida final está disponible al final del pulso de reloj.

construcción

Un flip-flop JK maestro-esclavo es una cascada de dos flip-flops SR con retroalimentación desde la salida del esclavo a la entrada del maestro. El circuito flip-flop maestro-esclavo se muestra a continuación.

El pulso de reloj positivo se aplica al flip-flop maestro y se invierte antes de aplicarse al esclavo. Es decir, el flip-flop maestro está activo durante las transiciones positivas y el flip-flop esclavo está activo durante las transiciones negativas. Durante el flanco positivo del reloj, los datos de las entradas J y K pasan al flip-flop maestro y se mantienen allí hasta que se produce una transición de flanco negativo del reloj. Luego, los datos o la información se pasan al flip-flop esclavo, donde se recopila la salida.

A continuación se muestra la representación simbólica de un flip-flop JK maestro-esclavo con dos flip-flops JK.

A continuación se muestran la tabla de verdad y las entradas preestablecidas y claras para Master – Slave JK Flip – Flop.

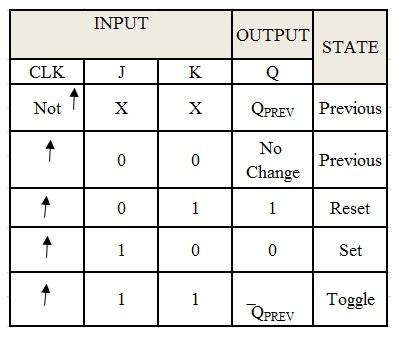

Cuando la entrada del reloj es Baja, las dos entradas del flip-flop maestro, es decir, las entradas J y K, no tienen ningún efecto en la salida del flip-flop maestro-esclavo.

Cuando la entrada del reloj es alta

- Si J es bajo y K es bajo: no hay cambio de estado.

- Si J es bajo y K es alto: el flip-flop maestro-esclavo está en estado de reinicio.

- Si J es alto y K es bajo: el flip-flop maestro-esclavo está configurado.

- Si J es alto y K es alto: alternar condición.

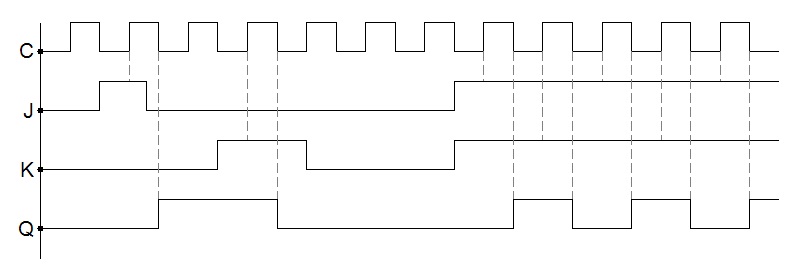

diagrama de tiempo

El ancho del pulso de entrada puede ser menor o mayor que el retardo de propagación del flip-flop, pero no afecta el estado de salida. Sin embargo, a menos que se violen los tiempos de configuración y retención, los valores de las entradas J y K en el momento del flanco positivo del reloj afectarán el estado de salida del flip-flop maestro-esclavo.

Volver a la cima

solicitud

El flip-flop JK es uno de los flip-flop más utilizados en electrónica digital. Esto se debe a sus funciones universalmente programables.

Las aplicaciones de las chanclas JK incluyen:

• Registro de turnos

• Divisor de frecuencia

• Cambio de aplicación

• Transferencia de datos paralela

• Transferencia de datos en serie

• Contador binario

• Detector de secuencia

Una de las aplicaciones de los flip-flops JK es la conmutación. Esto se explica a continuación.

Conmutación de flip-flop JK

Cuando se aplica una señal de reloj a un flip-flop JK, la transición ascendente de la señal del reloj de entrada permite cambiar la salida del estado actual. Este estado de habilitación no dura todo el ciclo positivo de la señal de reloj. Las entradas J y K del flip-flop no pueden provocar transiciones de pulsos de reloj. Sin embargo, la salida se determina según el valor de entrada en el momento del aumento. Esta es una de las aplicaciones del flip-flop JK. El comportamiento de salida del flip-flop JK con respecto a la transición ascendente del reloj se muestra a continuación utilizando formas de onda.

Volver a la cima

Artículo relacionado:

- Diseño flip-flop T | Circuito usando SR, JK, D…

- SR Flip-Flop – Diseño con puertas y aplicaciones

- Cómo voltear una imagen en Google Docs

- 555 Multivibrador astable mediante temporizador | Circuito,…

- Símbolos lógicos para puertas lógicas básicas (O, Y, NO,…)

- SRAM y DRAM | Comparación, estructura básica y diferencias