descripción general

Tabla de contenido

significado:

Un pestillo es un circuito lógico electrónico con dos estados estables o un multivibrador biestable. Los pestillos tienen una ruta de retroalimentación para retener información. Entonces, un pestillo podría ser un dispositivo de memoria. Un pestillo puede almacenar un bit de información siempre que el dispositivo esté encendido. Cuando se activa la habilitación, el pestillo cambia la información almacenada tan pronto como cambia la entrada. En otras palabras, el pestillo es un dispositivo activado por nivel. Cuando la señal de habilitación está activada, muestrea la entrada continuamente.

Los circuitos de enclavamiento funcionan en dos estados, activo-alto o activo-bajo, dependiendo de si la señal de disparo es alta o baja.

- Para circuitos de enclavamiento activo-alto, ambas entradas suelen ser bajas. Este circuito se activa por un nivel alto momentáneo en cualquiera de las entradas.

- Para circuitos de enclavamiento activo-bajo, ambas entradas suelen ser altas. Este circuito se activa por un nivel bajo momentáneo en cualquiera de las entradas.

pestillo SR

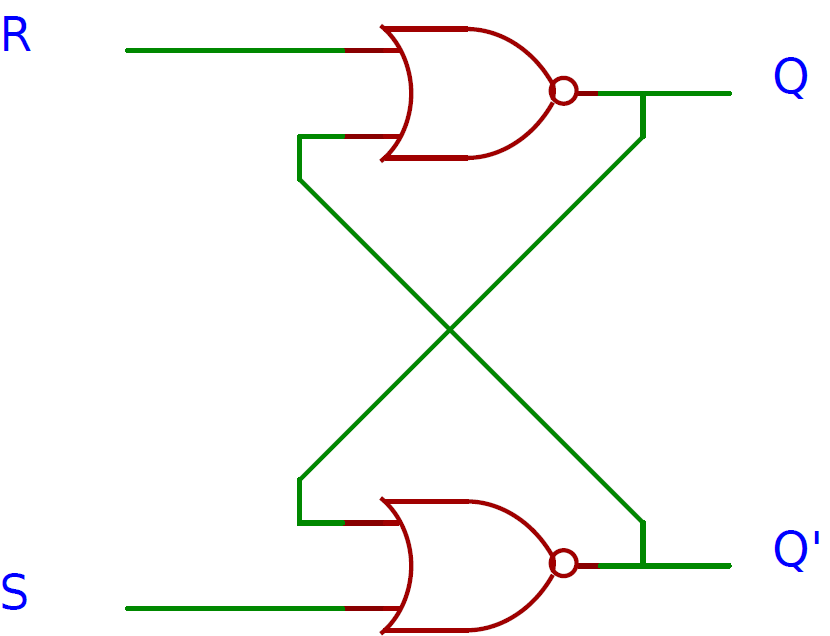

Las puertas estáticas se pueden utilizar como bloques de construcción básicos para construir pestillos simples. También se puede construir con dos puertas NOR introduciendo retroalimentación en el circuito de la puerta NOR.

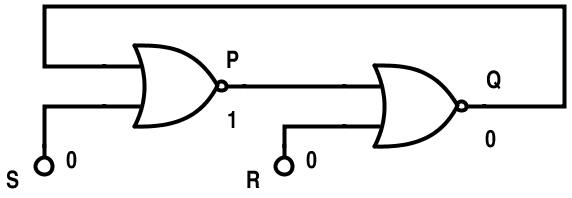

A continuación se muestra una lógica de puerta NOR simple con retroalimentación.

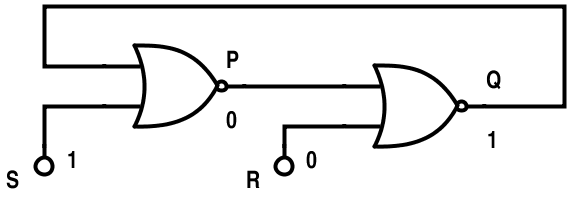

Aquí, las entradas S y R son ambas 0 (S = R = 0). La salida de la primera puerta NOR es P = 1. Esto se alimenta a la segunda puerta NOR con R = 0. Por tanto, la salida de la segunda puerta será Q = 0. Se dice que el circuito está en estado estacionario cuando P = 1. Si establecemos S = 1, entonces P = 0. Esto da como resultado Q =1 como se muestra a continuación.

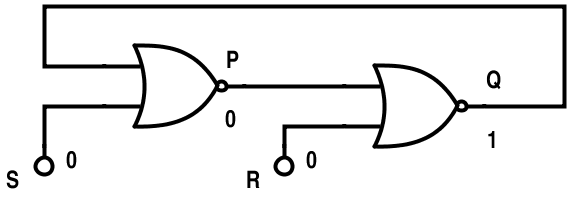

También se encuentra en condiciones estables. Si establecemos S en 0, Q = 1 se retroalimenta al primer NOR y P permanece en 0, por lo que no hay cambios. Esto se muestra en la siguiente figura.

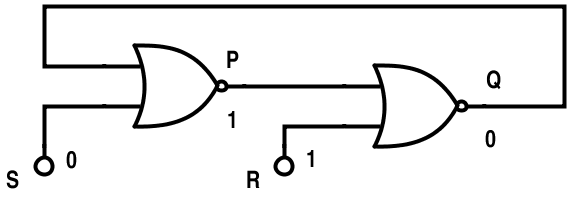

Cuando R se convierte en 1, Q se convierte en 0 y P vuelve a 1.

Si R se establece en 0, no habrá cambios y regresará al punto de partida.

Se dice que un circuito tiene memoria porque su salida depende no sólo de la entrada actual sino también de un conjunto de entradas pasadas. Si no se permite la condición de entrada S = R = 1, las salidas en estado estacionario siempre serán complementarias. Si tanto S como R son iguales a 1, entonces P = 0 y Q = 0, lo que contradice la condición de complementariedad. Por lo tanto, se dice que la condición de entrada S = R = 1 no está permitida. Los circuitos de pestillo siempre se dibujan en forma cruzada para enfatizar la simetría entre las puertas.

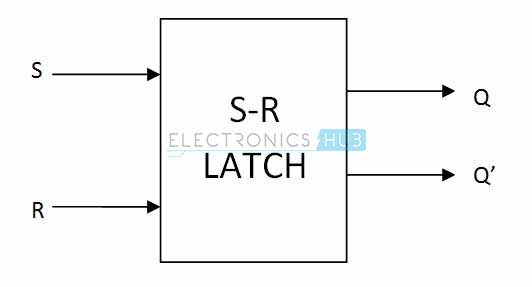

Este circuito “establece” la salida Q a 1 cuando S = 1, y “restablece” la salida Q a 0 cuando la entrada R = 1. Debido a la restricción S = R = 1, este circuito se llama: un juego: pestillo de reinicio (pestillo SR).

Volver a la cima

carrera alrededor de la condición

En los circuitos lógicos, una condición de carrera se refiere a una situación en la que dos entradas de un circuito lógico cambian simultáneamente y la salida cambia temporalmente. Los insumos compiten para cambiar los productos. Esto suele ocurrir en dispositivos que tienen salidas como entradas de retroalimentación al circuito. Esta es una situación indeseable que ocurre cuando un dispositivo intenta realizar dos operaciones al mismo tiempo (es decir, cambia el estado de dos entradas al mismo tiempo). Hay varias formas de evitar las condiciones de carrera, incluido el uso de disparadores de borde y flip-flops maestro-esclavo.

Volver a la cima

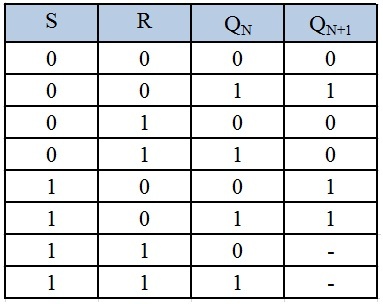

Tabla de transición de estado de bloqueo SR o tabla de verdad

Las tablas de estado son similares a las tablas de verdad en circuitos combinacionales que brindan información sobre el estado del circuito. Debido a que las salidas de los circuitos secuenciales dependen del estado actual y anterior, estas se representan en forma de tablas llamadas tablas de estados, que indican el siguiente estado en función del estado actual y otras entradas.

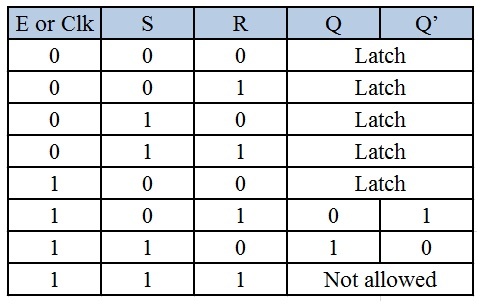

La tabla de estado del pestillo SR se muestra a continuación.

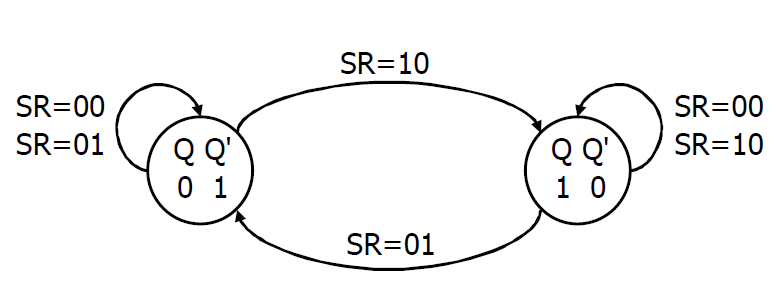

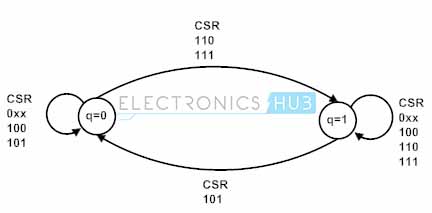

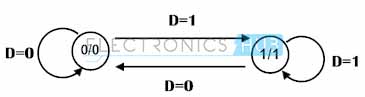

Diagrama de estado

Además de tablas y ecuaciones, las máquinas (o sistemas) de estados se pueden representar mediante diagramas de estados. En este diagrama de estados, los estados están representados por círculos y las transiciones entre estados están representadas por líneas o arcos que conectan los círculos. A continuación se muestra el diagrama de estado para un pestillo SR simple.

Un diagrama de estados proporciona toda la información que puede tener una tabla de estados. Esto se toma directamente de la tabla de estados.

Pestillo SR cerrado

Los pestillos son generalmente transparentes. Es decir, cuando la entrada cambia, la salida cambia inmediatamente. Sin embargo, en muchas aplicaciones es deseable tener un período de aislamiento en el que la salida no cambie cuando cambia la entrada. Durante este período, se dice que la salida está verdaderamente “bloqueada”. Esto se puede lograr mediante el uso de entradas adicionales (habilitaciones, relojes o puertas). Si no se afirma la señal de habilitación (o reloj o puerta), la entrada se ignora y la salida se retiene en su valor anterior. Para utilizar esta señal adicional, debe agregar lógica adicional. Estos circuitos se denominan pestillos de puerta o pestillos de reloj.

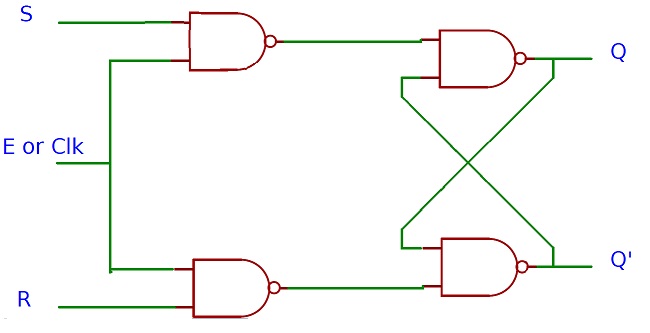

Los pestillos Gate SR se pueden crear de dos maneras. Una es agregar una puerta AND de segundo nivel al pestillo SR, y la otra es agregar una puerta NAND de segundo nivel al pestillo ̅S ̅R (pestillo SR invertido).

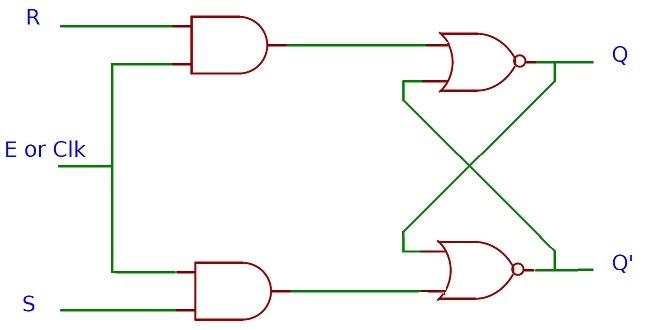

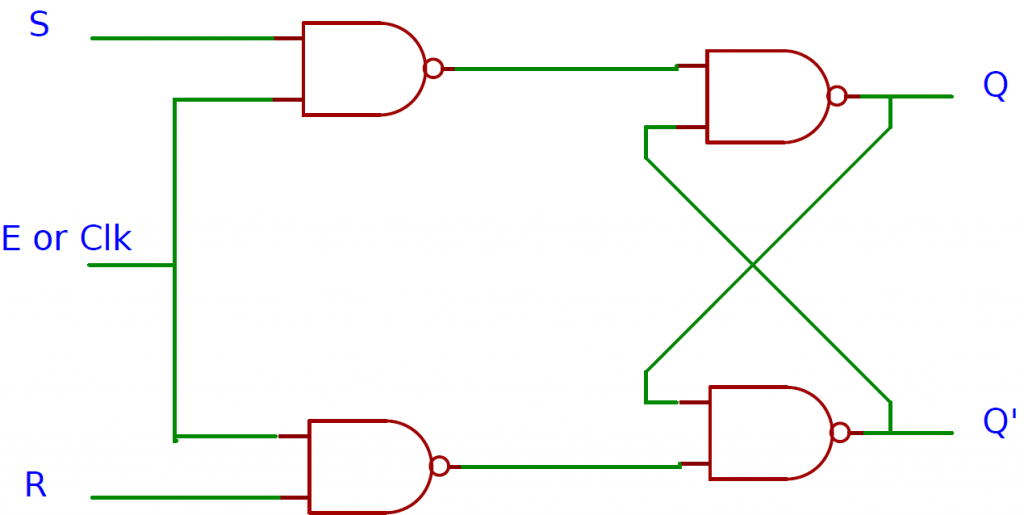

A continuación se muestra el esquema de un pestillo Gated SR hecho de puertas NOR.

A continuación se muestra el esquema de un pestillo Gated SR hecho de puertas NAND.

Cuando la puerta NAND invierte su entrada, el pestillo ̅S ̅R se convierte en un pestillo SR cerrado.

Si la habilitación (o el reloj) es Alta, se dice que el pestillo está habilitado. Es decir, la salida responde a la entrada.

Cuando la habilitación (o el reloj) está baja, el pestillo se desactiva y permanece en ese estado hasta que se afirma la habilitación.

El símbolo del pestillo SR de la puerta se muestra a continuación.

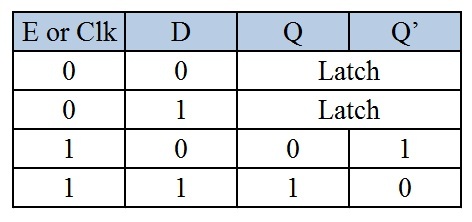

A continuación se muestra la tabla de verdad para el pestillo SR de la puerta.

A continuación se muestra el diagrama de estado del pestillo SR de la puerta.

Volver a la cima

pestillo D

Un bloqueo de datos o bloqueo de retardo (bloqueo D) es un tipo simple de bloqueo para almacenar datos. También llamado pestillo transparente. Se puede construir un pestillo en D simple con dos puertas NAND.

La condición de carrera en el pestillo SR que ocurre cuando S = R = 1 se evita en el pestillo D porque la entrada R se reemplaza con una S invertida y se le cambia el nombre a D. Por lo tanto, no existen insumos ilegales o prohibidos. En un pestillo D, Q siempre es D.

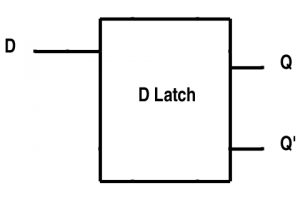

El símbolo del pestillo D se muestra a continuación.

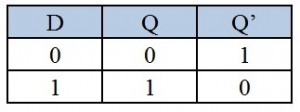

Estos pestillos en D simples no se usan con frecuencia, pero los pestillos en D con compuerta son muy comunes. A continuación se muestra la tabla de verdad para un pestillo D simple.

Volver a la cima

Pestillo de la puerta D

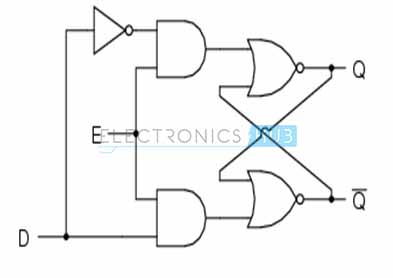

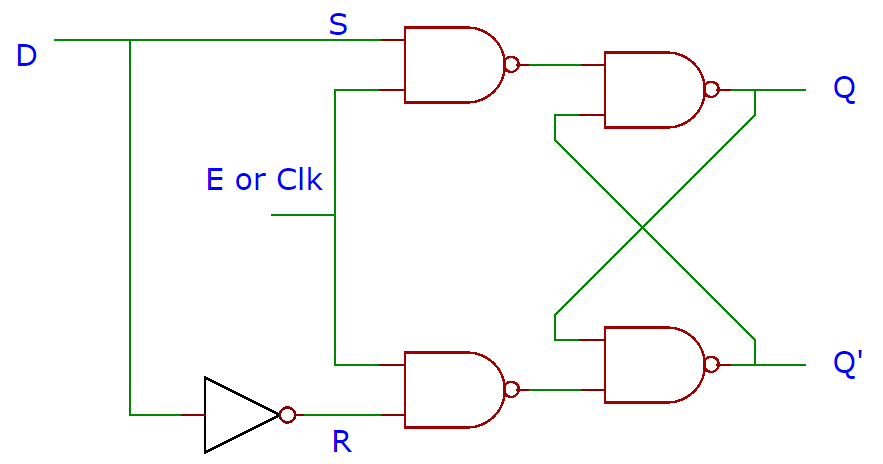

Un pestillo de puerta D se construye fácilmente modificando el pestillo SR de la puerta. El único cambio en el pestillo SR de la puerta es que la entrada R debe cambiarse a una S invertida. A continuación se muestra un pestillo de puerta formado a partir de un pestillo NOR SR.

Cuando el reloj o la habilitación están altos (lógica 1), la salida bloquea lo que esté en la entrada D. Si la habilitación o el reloj es bajo (0 lógico), la última entrada D alta habilitada se convierte en la salida.

Este circuito de enclavamiento nunca está en una condición de “carrera” porque una única entrada D está invertida y alimenta a ambas entradas. Por lo tanto, no es posible que existan las mismas condiciones de entrada. Por lo tanto, los circuitos D-latch se pueden utilizar de forma segura en cualquier circuito.

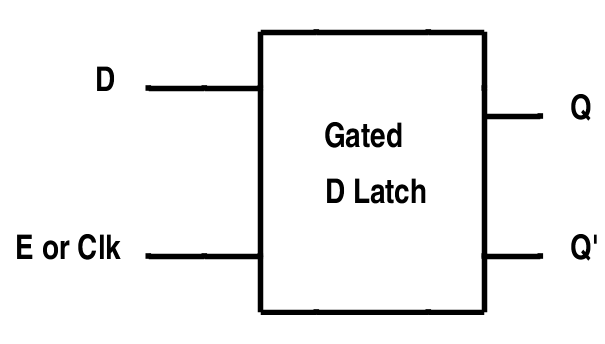

El símbolo del pestillo de la puerta D se muestra a continuación.

De manera similar a los pestillos cerrados NOR SR, los pestillos cerrados D también se pueden construir a partir de pestillos cerrados NAND SR. A continuación se muestra el circuito para un pestillo D cerrado desde un pestillo NAND SR cerrado.

Puedes utilizar una puerta NAND para obtener el valor invertido, evitando así el uso de un inversor. El circuito anterior requiere algunas modificaciones. El circuito resultante se muestra a continuación.

A continuación se muestra la tabla de verdad (o tabla de estado) para el pestillo de la puerta D.

A continuación se muestra el diagrama de estado del pestillo de la puerta D.

Volver a la cima

solicitud

- Estos son dispositivos de memoria básicos de 1 bit.

- Los pestillos D se utilizan comúnmente como puertos de E/S en sistemas asíncronos.

- Los enclavamientos de datos a veces se utilizan en sistemas bifásicos síncronos para reducir el número de transistores.

Volver a la cima

Ventajas de los pestillos

- Los pestillos son rápidos porque no tienen que esperar una señal de reloj y se usan más en diseños de alta velocidad.

- Se requiere menos energía.

- Los diseños basados en pestillos tienen tamaños de troquel más pequeños.

- La principal ventaja de los pestillos es el “préstamo de tiempo”. Un método para tomar prestado el tiempo necesario para realizar una operación de otras operaciones si la operación no se completa a tiempo.

Volver a la cima

Desventajas de los pestillos

- Los pestillos son menos predecibles porque es más probable que afecten las condiciones de carrera.

- Dado que es un dispositivo sensible al nivel, es más probable que se produzca metaestabilidad.

- Los circuitos de retención son difíciles de analizar debido a sus características sensibles al nivel.

Volver a la cima

Artículo relacionado:

- Diseño flip-flop T | Circuito usando SR, JK, D…

- SR Flip-Flop – Diseño con puertas y aplicaciones

- ¿Qué es un demux?

- Símbolos lógicos para puertas lógicas básicas (O, Y, NO,…)

- Conceptos básicos del disparador Schmitt | ¿Cómo funciona un disparador Schmitt?

- Tipos de diseño de circuitos ADC | Flash, sucesivos…