En tutoriales anteriores, analizamos codificadores binarios que codifican los datos proporcionados. Sin embargo, una limitación de los codificadores digitales estándar es que producirán errores en la salida si más de una entrada está activa en un momento dado. Si dos entradas son 1 lógica al mismo tiempo, se produce una combinación de salidas indefinida.

Considere el caso de un codificador de 8 a 3 líneas. Si D2 y D5 son 1 al mismo tiempo, el codificador produce una salida de 111. Esto significa que las tres salidas son iguales a 1 lógico (por ejemplo, si la persona que maneja el teclado presiona la segunda tecla antes de soltar la primera). Este valor no corresponde al binario 2 ni al binario 5.

Para solucionar este problema, el circuito codificador debe establecer prioridades para que en tales casos sólo se codifique una entrada. Esto significa que los niveles de cada entrada deben priorizarse de modo que siempre que dos entradas sean iguales a 1 lógico al mismo tiempo, el codificador produzca una salida correspondiente a la entrada de mayor prioridad. Un codificador de este tipo se denomina codificador prioritario.

Volver a la cima

descripción general

Tabla de contenido

codificador de prioridad

Como se mencionó anteriormente, un codificador de prioridad es un tipo de codificador en el que se impone un orden en la entrada. Es decir, incluye una función de prioridad respecto a los codificadores estándar.

Sin embargo, esta prioridad se basa en la magnitud relativa de los insumos. Por lo tanto, las entradas con magnitudes mayores se codifican primero.

Un codificador de prioridad puede seleccionar la entrada con mayor prioridad en muchas aplicaciones prácticas. Este proceso de selección se llama arbitraje.

Uno de los ejemplos más comunes de arbitraje es cuando un sistema informático tiene muchos dispositivos de entrada y algunos de ellos intentan suministrar datos a la computadora al mismo tiempo. En estos casos, el codificador de prioridad habilita el dispositivo de entrada con mayor prioridad entre los dispositivos que intentan acceder a la computadora al mismo tiempo.

Veamos un diseño de codificador de prioridad de 4 y 8 entradas.

Volver a la cima

simple Codificador de prioridad de 4 entradas

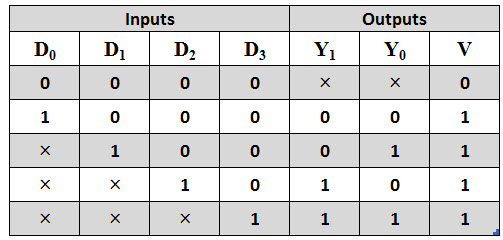

Este codificador de prioridad consta de cuatro entradas y tres salidas. Hay dos codificadores,norte Tiene una entrada y n salidas, y hay una tercera salida ‘V’ que es un indicador de bit válido y se pone a 1 cuando una o más entradas están activas o son iguales a 1.

Este bit válido es 0 si todas las entradas son 0. Esto indica que no hay ninguna entrada válida. En esta condición, otras salidas se consideran condiciones indiferentes y no se examinan si V es cero.

Según la tabla de verdad, las entradas con números de subíndice más altos tienen la máxima prioridad. El bit más significativo tiene la prioridad más alta y el bit menos significativo tiene la prioridad más baja.

En la tabla de verdad, D3 tiene la prioridad más alta y D0 tiene la prioridad más baja. Si D3 está activo o 1, la salida será 11, independientemente del resto de entradas. La siguiente prioridad más alta es D3 seguida de D2.

La siguiente prioridad más alta después de D1 es D2. Entonces, si D3 es 0 y D2 es 1, la salida será 10, independientemente de las otras dos entradas (que tienen menor prioridad). Si la entrada de mayor prioridad es 0, se produce la salida de D1, y así sucesivamente, con niveles de prioridad más bajos.

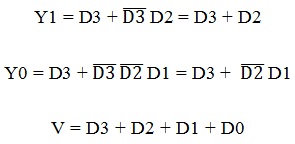

De la tabla de verdad anterior, podemos escribir una expresión booleana para las dos salidas de la siguiente manera:

Simplificación del mapa K

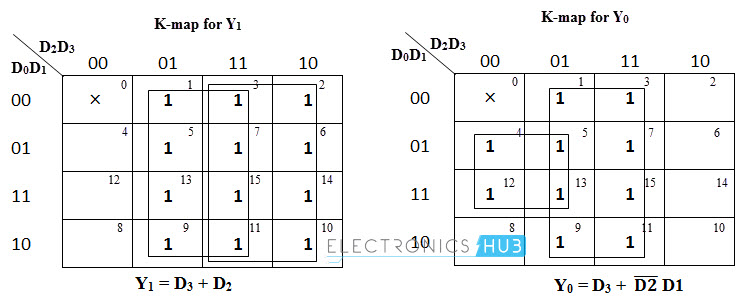

Las expresiones anteriores para entradas y salidas válidas se pueden obtener utilizando la simplificación de K-map. La tabla de verdad para este codificador se muestra en 5 filas, pero si reemplazamos cada × en cada fila primero con un 0 y luego con un 1, podemos obtener 16 combinaciones de entrada. El término mínimo de las dos salidas se puede derivar de la siguiente manera.

Y1 = ∑ metro (1, 2, 3, 5, 6, 7, 9, 10, 11, 13, 14, 15)

Y0 = ∑ metro (1, 3, 4, 5, 7, 9, 11, 12, 13, 15)

Luego obtenga el siguiente resultado del mapa K a continuación.

Y1 = D3 + D2

Y0 = D3 + (D2) ̅ D1

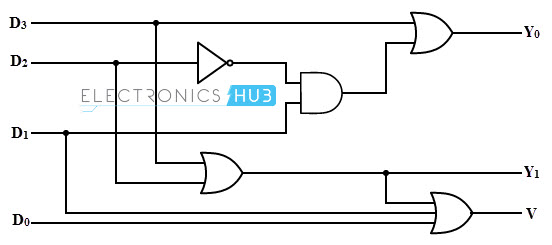

El diagrama lógico del codificador de prioridad de cuatro entradas se implementa mediante la expresión de salida correspondiente obtenida de la simplificación del mapa K. El diagrama de circuito de este codificador se muestra a continuación.

Volver a la cima

Codificador de prioridad 8 a 3 o codificador de prioridad octal a binaria

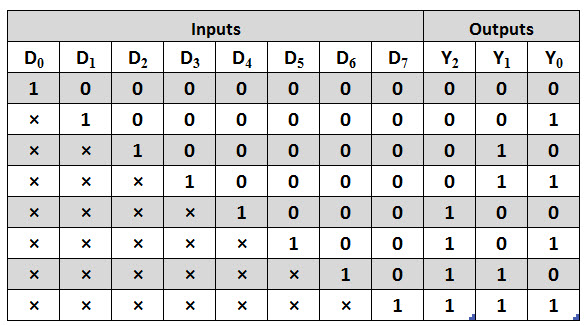

A continuación se muestra la tabla de verdad para el codificador de prioridad octal a binaria. Este tipo de codificador tiene 8 entradas y 3 salidas y produce un código binario correspondiente. A cada entrada se le asigna una prioridad, por lo que si dos o más entradas son 1 al mismo tiempo, la entrada con mayor prioridad aparecerá en la salida.

Supongamos que si las líneas de entrada D2, D4 y D7 son 1 lógico al mismo tiempo, independientemente de las otras entradas, entonces solo se codifica D7 y la salida es 111. De manera similar, si D3 = 1, los estados de D2, D1 y D0 son irrelevantes. No te preocupes, la salida será igual a 011.

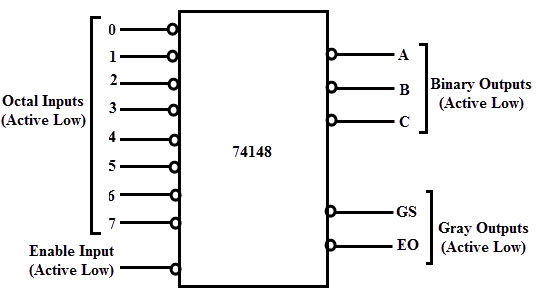

IC 74148 es un circuito codificador MSI más comúnmente utilizado como codificador de prioridad de 8 a 3 líneas. Las características principales de este codificador incluyen cascada para codificación de prioridad de n bits, conversión de código, codificación de prioridad de la línea de entrada de mayor prioridad, conversión de decimal a BCD, habilitación de salida cuando todas las entradas son altas – activas incluye baja, etc.

Las entradas de circuitos digitales suelen utilizar códigos octales, por lo que estas largas palabras binarias deben ingresarse manualmente. Por lo tanto, los circuitos integrados de codificador están diseñados para lograr dicha operación.

La siguiente figura muestra su diagrama de pines y tiene una entrada baja activa y una salida baja activa. Para manejar más entradas, estos circuitos integrados se conectan en cascada habilitando entradas y salidas grises que también son líneas bajas activas.

Volver a la cima

Codificador de prioridad decimal a BCD

Este tipo de codificador realiza las mismas operaciones que un codificador de decimal a BCD normal al codificar un número decimal en una salida BCD de 4 bits. Sin embargo, consta de características adicionales que brindan prioridad. Es decir, la salida BCD se produce correspondiente a la prioridad más alta de los dígitos decimales que aparecen en la entrada, independientemente de todas las demás entradas.

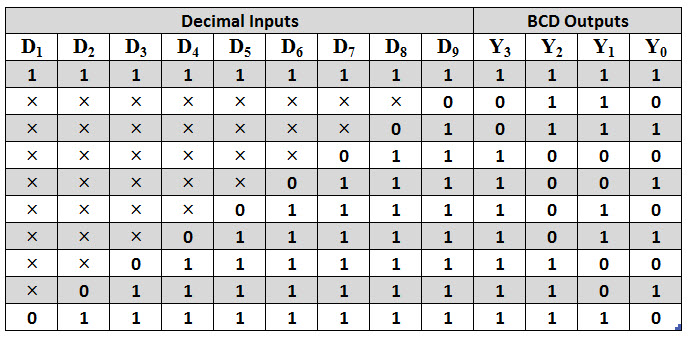

La siguiente figura muestra la tabla de verdad para un codificador de decimal a BCD. Este codificador tiene nueve entradas bajas activas que representan dígitos decimales del 1 al 9. Se genera un código BCD invertido según la entrada superior activada.

Si todas las entradas de D1 a D9 son 1 lógico, todas las salidas se configuran en el inverso de 0000, 1111 o un código BCD de 0. Si D9 es 1, la salida será 0110, la inversa de 1001. Ese es un código BCD de 9. Este procedimiento es el mismo para todos los números decimales.

La salida normalmente es Alta cuando no hay ninguna entrada activa, lo que corresponde a una entrada de 0 decimal. Por lo tanto, cuando todas las entradas están en Alto, se considera que el codificador está en un estado decimal 0 porque no hay ninguna entrada D0.

Además, si dos entradas están activas al mismo tiempo, digamos D3 y D5, la prioridad más alta de estas entradas, D5, se codificará como 1010, que es la inversa de 0101. Por este motivo, este codificador se denomina codificador prioritario.

Volver a la cima

Codificador de 16 a 4 prioridades

De manera similar, se puede construir un codificador de 16 a 4 utilizando seis codificadores de 4 a 2. Los cuatro codificadores de 4 a 2 están conectados a las 16 entradas y las 8 salidas se conectan nuevamente a los dos codificadores de 4 a 2 para producir 4 salidas.

Aplicación del codificador de prioridad.

En comparación con los codificadores digitales estándar, los codificadores de prioridad se utilizan con mayor frecuencia en varias aplicaciones. Los codificadores de mayor prioridad se diseñan conectando en cascada varios codificadores de prioridad. Por lo tanto, este tipo de codificador se utiliza para reducir la cantidad de conexiones requeridas en ciertas aplicaciones donde hay múltiples entradas presentes.

codificador de teclado

Supongamos que el teclado QWERTY está conectado a una microcomputadora, por lo que la computadora necesita leer las 104 teclas del teclado y leer que solo se presiona una tecla en un momento dado como Alta o Baja.

No es posible conectar todas las 104 conexiones directamente a la computadora (si está mal configurada), pero es más eficiente conectarlas usando un codificador prioritario. Con este codificador, cada carácter o clave se codifica en un código ASCII estándar de 7 bits (decimal 0-127).

Todas estas 104 teclas o botones individuales. Luego ingrese el código BCD de 7 bits en su computadora. Uno de esos tipos de codificador de teclado es el 74C923 de 20 teclas. Estos codificadores también tienen funciones de prioridad, como dar la entrada de mayor prioridad cuando se presionan dos teclas al mismo tiempo.

codificador de posición

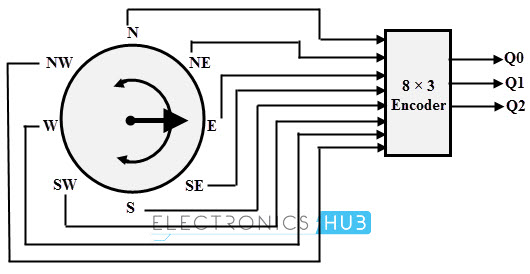

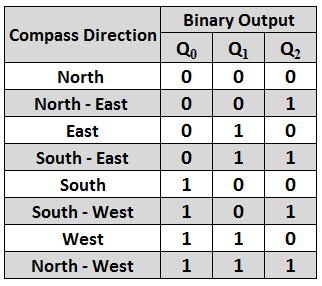

El control de posición magnético es otra aplicación común para los codificadores de prioridad. Estos controles se utilizan para posicionar brazos robóticos y navegar barcos. En estos casos, el codificador convierte la posición angular o rotacional de la brújula en un código digital. Luego, este código se ingresa en la computadora para proporcionar datos de navegación.

La siguiente figura muestra un codificador de brújula simple que convierte 8 posiciones en una salida de 3 bits. Este tipo de configuración de entrada/salida utiliza el IC 74LS148, que es un codificador de prioridad de línea de 8 a 3. Los interruptores de láminas y los imanes se utilizan comúnmente para indicar la posición angular de una brújula.

Volver a la cima

Artículo relacionado:

- SR Flip-Flop – Diseño con puertas y aplicaciones

- Sumador binario y restador binario

- Generador de paridad y verificación de paridad

- ¿Qué es un demux?

- Símbolos lógicos para puertas lógicas básicas (O, Y, NO,…)

- Tipos de diseño de circuitos ADC | Flash, sucesivos…