prólogo

Los sistemas de voltaje mixto de hoy en día a menudo usan la traducción de nivel bidireccional como una forma de mejorar la eficiencia y ahorrar energía. Hay varias formas de implementar la conversión bidireccional, pero una de las más fáciles es usar un dispositivo lógico estándar con un pin de dirección (DIR). Varias familias lógicas admiten esta función, incluidas muchas versiones de la lógica GTL y LVTTL. Agregar una función de retención de autobús ayuda a proteger su dispositivo.

obtener un sentido de dirección

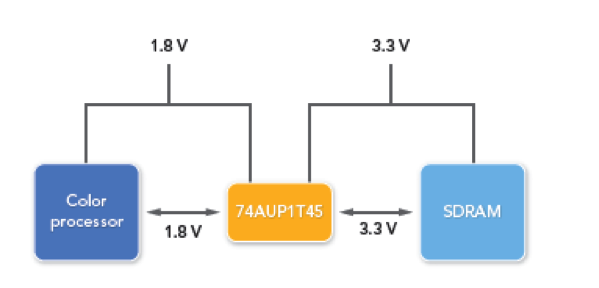

Los dispositivos lógicos que convierten voltajes de bajo a alto o de alto a bajo también transfieren datos. La transferencia de datos puede funcionar en una dirección (unidireccional) o en dos direcciones (bidireccional). Los traductores de voltaje con dos voltajes de suministro, cada uno compatible con un rango de voltaje diferente, se pueden usar para la traducción de bajo a alto o de alto a bajo y, por lo general, están disponibles en versiones que admiten la traducción de nivel unidireccional o bidireccional. Algunos traductores bidireccionales tienen un pin de dirección (DIR) que controla la dirección de los datos. Establecer el pin DIR establece la dirección de conversión del puerto A al puerto B o del puerto B al puerto A. La Figura 1 muestra una cámara digital que usa el NXP 74AUP1T45 para convertir señales entre un procesador de color que usa una señal de 1,8 V y un subsistema de memoria que usa una señal de 3,3 V. El 74AUP1T45 es un transceptor de un solo bit con dos E/S de datos (A y B), una entrada de control DIR y pines de fuente de alimentación doble (VCC(A) y VCC(B)). Tanto VCC(A) como VCC(B) se pueden alimentar con cualquier tensión entre 1,1 V y 3,6 V, lo que convierte a este dispositivo en una interfaz entre cualquier nodo de baja tensión (1,2, 1,5, 1,8, 2,5 o 3,3 V). Una señal alta en DIR permite la transmisión de A a B, y una señal baja en DIR permite la transmisión de B a A.

Los traductores bidireccionales con pines DIR están disponibles en muchos proveedores de lógica estándar. Por ejemplo, las familias AUP, AVC, LVC y ALVC de NXP admiten diseños de voltaje mixto que van de 0,8 a 5,5 V. La señal de salida de un dispositivo se puede traducir de alto a bajo o de bajo a alto según sea necesario para que coincida con la entrada. límite. Las opciones incluyen formatos de 1, 2, 4, 8 o 16 bits que cubren rangos de conversión de 0,8 a 3,6 V y de 1,2 a 5,5 V. Estos resultados son 1,2, 1,8, 2,5, 3,3 y 5,0 V. Otra cosa que debe buscar en un dispositivo con un pin DIR es que tenga un circuito IOFF incorporado. Esto elimina el daño por reflujo cuando la salida se desactiva durante el modo de suspensión o apagado. En la mayoría de los casos, el dispositivo con el pin DIR es el dispositivo activo. Es decir, tiene una etapa de salida CMOS con corrientes de fuente y sumidero específicas.

circuito de espera de autobús

Algunos traductores bidireccionales, especialmente los traductores bidireccionales de la familia CMOS más nuevos, también están equipados con un circuito de retención de bus (Figura 2) que garantiza un nivel lógico definido cuando la entrada está flotando. Esto evita que el voltaje de entrada fluctúe cerca del voltaje de umbral, lo que puede dañar el dispositivo.

Los productos NXP con una “H” en el número de modelo están equipados con un circuito de retención de bus. El circuito de retención de bus activo de las familias NXP LVC y AVC evita las entradas flotantes al mantener las entradas de datos no utilizadas en un nivel lógico válido. El circuito de retención de bus actúa como un latch de entrada, reteniendo los últimos datos activados si las entradas se mantienen triestablecidas o de alta impedancia. El estado lógico del pestillo de retención de bus no está garantizado cuando se aplica energía por primera vez. Puede encenderse alto o bajo. También se requieren resistencias externas si se desea el estado lógico predeterminado. Estas resistencias deben dimensionarse para sobrecargar la corriente de retención del bus de entrada para evitar problemas de contención.

Traductores y transceptores de nivel GTL a LVTTL

Gunning Transceiver Logic (GTL) es un tipo de señal lógica que se utiliza para controlar los buses de backplane electrónicos. Definido en el estándar JESD 8-3 de JEDEC, GTL tiene una oscilación de voltaje de 0,4 a 1,5 V, mucho menor que los voltajes utilizados en la lógica TTL y CMOS, y realiza una terminación resistiva en paralelo simétrico. GTL se encuentra comúnmente en buses frontales basados en arquitectura Intel. Para que las señales GTL sean compatibles con el resto del sistema, los niveles GTL deben convertirse a TTL de bajo voltaje (LVTTL). NXP ofrece una gama completa de traductores y transceptores dedicados para el formato GTL.

Conclusión

El pin DIR establece la dirección del flujo de datos y se puede utilizar para implementar la traducción de nivel bidireccional. Algunas familias lógicas diseñadas para la conversión de voltaje de uso general en el rango de 0,8 V a 5,5 V incluyen un pin DIR que se puede usar para la conversión bidireccional. Un dispositivo con un circuito de retención de bus ayuda a proteger el dispositivo del daño causado por el voltaje de entrada que se acerca al umbral máximo. Muchos traductores de nivel GTL diseñados específicamente para admitir la lógica GTL comúnmente utilizada en los procesadores tienen un pin DIR que se puede usar para traducir niveles GTL a niveles LVTTL. *DESCARGA GRATUITA* Nuestra nueva guía de 30 páginas explora varias técnicas para administrar diseños de voltaje mixto y brinda recomendaciones detalladas de productos.