Desde el surgimiento del silicio (Si) como material dominante para la fabricación de circuitos integrados en la década de 1960, ha habido interés en reemplazarlo con un semiconductor más ideal. Los diversos argumentos para reemplazar el Si están dominados por la urgencia de una mayor escala (es decir, miniaturización, reducción) del dispositivo fundamental de los circuitos integrados, el transistor de efecto de campo semiconductor de óxido de metal de silicio (MOSFET), que no es factible.

Desde el surgimiento del silicio (Si) como material dominante para la fabricación de circuitos integrados en la década de 1960, ha habido interés en reemplazarlo con un semiconductor más ideal. Los diversos argumentos para reemplazar el Si están dominados por la urgencia de una mayor escala (es decir, miniaturización, reducción) del dispositivo fundamental de los circuitos integrados, el transistor de efecto de campo semiconductor de óxido de metal de silicio (MOSFET). El escalado de transistores está impulsado por el deseo de aumentar la densidad de transistores en un chip para mejorar el rendimiento informático. Los nanotubos de carbono de pared simple (CNT), compuestos por una sola capa atómica de átomos de carbono dispuestos hexagonalmente, enrollados en cilindros sin costura de 1 a 2 nanómetros de diámetro, son los principales candidatos para reemplazar el silicio. Este artículo describe brevemente la motivación del proyecto actual de IBM para continuar considerando los CNT para futuras tecnologías informáticas de bajo voltaje y alto rendimiento.

El fin de la ley de Moore para Si

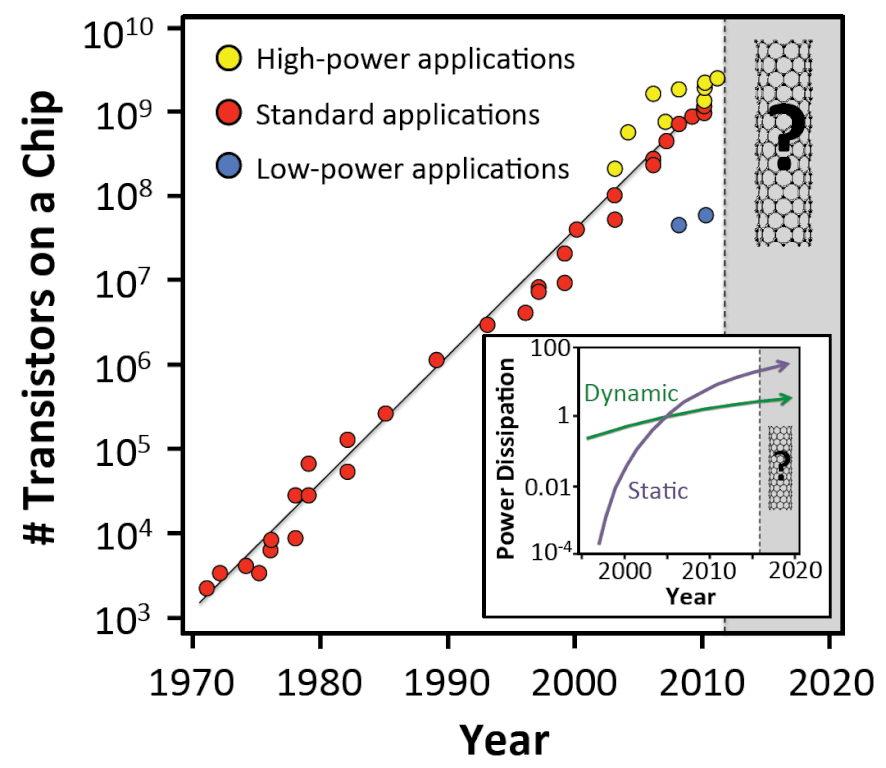

En un artículo de investigación de 1965, uno de los eventuales fundadores de Intel, Gordon Moore, hizo observaciones y predicciones sobre las tasas de escalado de los transistores. Su simple predicción en realidad se convirtió en un decreto que movió la industria conocido como “Ley de Moore”. En pocas palabras, la cantidad de transistores en un chip se duplica aproximadamente cada dos años (el período de tiempo ha cambiado varias veces entre uno y dos años), como se muestra en la gráfica de la Figura 1. Está estipulado. Con una innovación constante, los MOSFET de Si han seguido el ritmo de las predicciones de Moore, pero existe una aceptación generalizada de que el final está cerca, incluso dentro de los próximos años. Lo más interesante es que la desaparición del escalado de MOSFET de Si no se debe necesariamente a la incapacidad de fabricar transistores más pequeños. Más bien, significa que los transistores escalados se comportan muy mal y la potencia es demasiado alta. Como señaló John Markoff en un artículo reciente del New York Times,

“El problema no es que no podamos meter más transistores en un chip. Ciertamente es posible, pero como una ciudad que no puede alimentar todo un sistema de alumbrado público, es demasiado hacer funcionar todos los transistores económicamente. Puede requerir un mucho poder”. [1]

De hecho, es seguro decir que la Ley de Moore lleva más de una década muerta, como lo estuvo durante los primeros 40 años. Como se muestra en la Figura 1, las desviaciones de la ley se hacen comúnmente para cumplir con las necesidades específicas de la aplicación (alta o baja potencia/rendimiento). Además, la demanda de computación más rápida y eficiente ya no está ligada principalmente al escalado de transistores, sino que se centra cada vez más en el nivel arquitectónico (como los procesadores multinúcleo).

¿Por qué nanotubos de carbono?

La lucha por mantener el Si en línea con la escala del transistor proyectada es cada vez más evidente. La última gran migración para mantener Si [2] La tecnología de 2012 es la transición de dispositivos planos a estructuras de aletas 3D (o tri-puerta). Sin embargo, incluso si las aletas de Si son seguidas por nanocables de Si, es poco probable que se logren los límites de escala tanto de la longitud de la puerta (~10 nm) como del voltaje de suministro (~0,8 V), métricas clave que se reducirán en los nodos tecnológicos futuros. Superar. De hecho, los apocalípticos de Si han existido durante años, y la innovación siempre ha demostrado que estaban equivocados. Sin embargo, cada avance tecnológico revela las deficiencias fundamentales de Si, que son cada vez más difíciles de resolver. Considere la gráfica de consumo de energía en el recuadro de la Figura 1. Hemos llegado a un punto en el que la energía estática (cuando el transistor está apagado) es más costosa que la energía dinámica (estado encendido). Este fenómeno se conoce como transistor de fuga y es principalmente el resultado de la pérdida de control de corriente en dispositivos de dimensiones muy pequeñas. Para CNT con un espesor de cuerpo de canal de solo alrededor de 1 nanómetro (10 átomos), la puerta del transistor puede controlar de manera más efectiva la corriente en el canal, incluso si las dimensiones se reducen considerablemente. Esta ventaja podría hacer que las tendencias futuras en el consumo de energía dinámico y estático sean más prometedoras, reduciendo ambas curvas que se ven en el recuadro de la Figura 1.

Una de las áreas de aplicación de más rápido crecimiento es la informática de bajo consumo. En esta área, la tensión de alimentación es más importante que el número de transistores, incluso a expensas del rendimiento. Los canales de nanotubos han demostrado una capacidad superior para operar a voltajes bajos que cualquier otro material demostrado, lo que los convierte en los principales candidatos para aumentar el número de transistores incluso para aplicaciones de baja potencia. Sin embargo, el espacio de aplicación potencial de los CNT no se limita a la baja potencia. La ampacidad sin igual de los nanotubos los hace igualmente atractivos para aplicaciones informáticas de alto rendimiento. Además, existe un espacio de aplicación hasta ahora desconocido para los circuitos integrados comerciales. Es una electrónica flexible y/o transparente. Con su transparencia casi perfecta a la luz visible, alta flexibilidad mecánica y total independencia del sustrato, los nanotubos se prestan a una miríada de aplicaciones exóticas que han sido irrealizables con semiconductores a granel como el Si.

La apuesta de IBM por la tecnología CNT

No todos los atributos prometedores de las futuras tecnologías digitales de CNT se hacen realidad sin algunos desafíos prácticos. El principal obstáculo es la dificultad de alinear los nanotubos con un paso constante y una ubicación precisa. Aunque el enfoque en este tema ha aumentado en los últimos años, se necesita mucho trabajo para alcanzar la meta de al menos 100 CNT por micrón. El segundo es la necesidad de un mejor control de calidad de los materiales. Los nanotubos pueden ser semiconductores o metálicos, por lo que necesitamos obtener materiales que sean lo más cerca posible del 100 % de semiconductores (en IBM, podemos llegar al 99,3 %). Finalmente, el propio transistor CNT necesita mejoras. Estos incluyen contactos optimizados, estructuras de puertas autoalineadas y capas de pasivación adecuadas.

A pesar del trabajo que queda por hacer, es sorprendente lo lejos que han llegado los transistores CNT en poco más de 13 años. Se han hecho enormes progresos tanto en el control de materiales como en la comprensión/mejora de los dispositivos. Comparar el progreso de la tecnología CNT con el de los primeros semiconductores a granel es bastante notable, como se muestra en la Figura 2. Cuando surgió la Ley de Moore, el progreso en el mundo de los circuitos integrados comenzó en un camino predeterminado. Desde 1998, este camino ha sido diseñado por un grupo llamado International Technology Roadmap for Semiconductors (ITRS). El ITRS planifica los entregables (dimensiones del dispositivo, rendimiento, etc.) requeridos para la tecnología con hasta 15 años de anticipación. [3]Por lo tanto, los transistores CNT no solo son superiores a los MOSFET de Si actuales. Más bien, debe funcionar significativamente mejor que cualquier dispositivo de Si posible para justificar el costo general de migrar a una nueva plataforma. Esto es lo que IBM está tratando de determinar actualmente.

El Centro de Investigación IBM TJ Watson cuenta con personal y equipo únicos para abordar los obstáculos restantes para la tecnología CNT. Internamente, sintetizamos, purificamos y separamos grandes cantidades de CNT semiconductores. Se están investigando activamente estrategias para mejorar la precisión de la colocación de nanotubos en obleas de 200 mm. También seguimos avanzando en nuestra comprensión del rendimiento y los límites de escala de los transistores CNT, incluida la optimización de estructuras de dispositivos técnicamente viables. ¿Significa todo esto que los CNT están garantizados en la hoja de ruta del circuito integrado para los próximos años? Pero sí garantiza que pronto tendremos una respuesta definitiva sobre si la tecnología de transistores CNT es posible y lo suficientemente práctica para impulsar la próxima revolución en la computación digital.

Referencias

[1] http://www.nytimes.com/2011/08…

[2] http://newsroom.intel.com/docs…

[3] http://www.itrs.net/