Un informe técnico anterior, Elección del dispositivo ESD adecuado, se centró únicamente en la idea de que el objetivo principal de un dispositivo ESD es proporcionar una ruta de derivación de resistencia mínima a GND. Esta idea proporcionó a los diseñadores de placas una forma de calcular la resistencia efectiva de un dispositivo de protección durante un transitorio de ESD. Esta resistencia, o resistencia dinámica, se puede usar para comparar y seleccionar el mejor dispositivo de la gran cantidad de componentes ESD en el mercado actual.

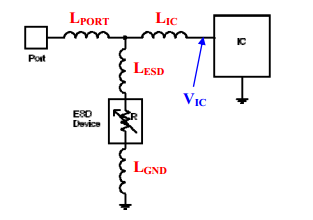

Un informe técnico anterior, Elección del dispositivo ESD adecuado, se centró únicamente en la idea de que el objetivo principal de un dispositivo ESD es proporcionar una ruta de derivación de resistencia mínima a GND. Esta idea proporcionó a los diseñadores de placas una forma de calcular la resistencia efectiva de un dispositivo de protección durante un transitorio de ESD. Esta resistencia, o resistencia dinámica, se puede usar para comparar y seleccionar el mejor dispositivo de la gran cantidad de componentes ESD en el mercado actual. Concluí el documento con la premisa simple de que, después de considerar todos los demás efectos parásitos, el dispositivo con la resistencia dinámica más baja le brinda al diseñador la mejor oportunidad de un diseño de primer paso exitoso.

Este informe técnico analiza varias técnicas que los diseñadores de placas pueden usar para lograr los niveles de ESD requeridos en sus diseños si el dispositivo de protección contra ESD de su elección no pasa las pruebas de ESD en el sistema.

Fondo

Hoy en día, muchos de los conjuntos de chips que se utilizan en los dispositivos electrónicos modernos, desde televisores LCD hasta teléfonos móviles, se desarrollan con tecnología de punta muy por debajo de los 130 nm. Estas tecnologías tienen una tolerancia mínima para voltajes de CC superiores a 3,3 V, por lo que un pulso ESD puede ser devastador para dichos dispositivos. Además, el requisito de protección ESD ‘a bordo’ o ‘en chip’ se ha reducido a 500 V, muy por debajo del requisito de campo típico de 8 kV.

Por lo tanto, los diseñadores de placas no solo necesitan protección ESD externa, sino que también deben asegurarse de que sea lo suficientemente robusta para tener en cuenta las vulnerabilidades del conjunto de chips de geometría pequeña. Como se mencionó en el documento anterior, colocar un dispositivo ESD con clasificación de 8 kV en una línea de datos protegida o un pin de E/S no garantiza que el conjunto de chips en sí supere los 8 kV durante la prueba en el sistema.

En muchos casos, los dispositivos ESD en sí mismos no brindan suficiente protección, lo que provoca una falla prematura del conjunto de chips. Este documento técnico proporciona algunas pautas que los diseñadores pueden usar para mejorar la protección ESD integrada.

¿Quiere ir tras bambalinas en la NASA? Littelfuse ha creado una experiencia de exploración y descubrimiento para la comunidad de ingenieros como parte del programa Speed2Design 2013. Los ingenieros de diseño galardonados tendrán la oportunidad de pasar tiempo con los ingenieros de la NASA en dos instalaciones de la NASA y aprender sobre lo último en tecnología espacial. Para más información y para participar, por favor visite: http://www.speed2design.com/.