Este artículo describe cómo se utilizan los procesadores Cortex™-M de ARM y los SoC CoreSight™ para diseñar microcontroladores multinúcleo. Este artículo analiza el diseño, los desafíos y los problemas relacionados con el uso de procesadores Cortex-M y SoC CoreSight.

Los diseños multinúcleo llegan a MCU

Algunas aplicaciones pueden beneficiarse de los diseños multinúcleo

- mayor rendimiento/rendimiento

- Agrupa tareas en tiempo real y no en tiempo real.

Motor de datos en tiempo real + protocolo de comunicación/GUI (por ejemplo, NXP LPC4300)

Tarea de control en tiempo real + procesador de aplicaciones (por ejemplo, Freescale Vybrid)

Procesador de aplicaciones + subsistema (OMAP)

- Por razones de confiabilidad, para separar las operaciones centrales críticas de las tareas “arriesgadas”. Esto también facilita la autenticación.

Desafíos de los sistemas multiprocesador

sistema de memoria

- AMBA® fue diseñado para admitir múltiples maestros de bus, pero…

- Memoria y ancho de banda de bus limitados

bajo consumo

- Los procesadores Cortex-M están diseñados para admitir varios modos de suspensión

- Los procesadores no utilizados pueden ponerse en modo de suspensión o apagarse

- Habilita la activación del reloj de los sistemas de bus y los componentes compartidos

- Se debe considerar el acceso desde el depurador

depurar

- La arquitectura de depuración de CoreSight permite compartir conexiones de depuración y rastreo

- Varios anchos de bus de seguimiento, dominios de reloj

Memoria – Programa ROM/Flash

- Los procesadores actuales de la serie Cortex-M no tienen caché*

- búsquedas frecuentes de instrucciones

- El flash suele ser lento en comparación con la velocidad del reloj de la CPU

- El bus es de 32 bits, muchas instrucciones son de 16 bits

- Cortex-M3 y Cortex-M4 tienen un búfer de instrucciones (3 palabras).

- Posibilidad de agregar caché a nivel del sistema

- Otros trucos de diseño de sistemas de memoria

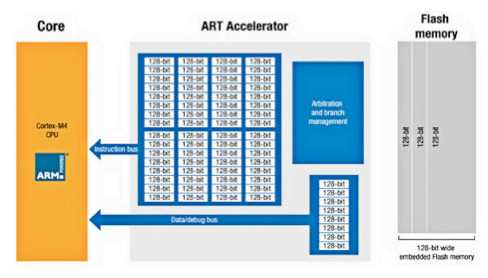

Acelerador de acceso flash

- flash de 64 o 128 bits

- unidad de captación previa

- caché de destino de rama

- Por ejemplo, STM32 F2/F4 es

- acelerador de ART

Uso compartido de ROM en un diseño simple de doble núcleo

Fácil uso compartido de la ROM del programa

Logró el 78 % del rendimiento ideal (Dhrystone 2.1, simulación Verilog)

Modificación de Arbitraje

Las recuperaciones literales de cualquiera de los núcleos mejoran ligeramente el rendimiento en un 78,9 %