Este artículo describe cómo diseñar y construir un oscilador de onda sinusoidal/cuadrada de dos rangos controlado por codificador ajustable. SLG47004 yo c

Se requiere un solo OPAMP para diseñar un oscilador sinusoidal analógico simple (utilizando la topología de puente de Wien) (consulte la Figura 1). Sin embargo, se requieren muchos más componentes activos y pasivos para diseñar un dispositivo completamente funcional con funcionalidad adicional. La Figura 2 muestra un esquema de un oscilador OPAMP con las siguientes características:

- Frecuencia ampliamente ajustable

- Dos velocidades de ajuste de frecuencia.Marcación rápida: marcación rápida y marcación lenta: para un ajuste de frecuencia preciso

- Dos rangos de frecuencias de salida de 15 Hz a 1,6 kHz y de 430 Hz a 36 kHz

- Onda sinusoidal con salida de onda cuadrada añadida

- Todos los controles usan un solo codificador con botones incorporados

- Consumo de energía muy bajo adecuado para el funcionamiento con baterías 3xLR44

- El consumo de energía muy bajo (0.8 uA) en el estado apagado elimina la necesidad de un interruptor físico (Nota 1)

- Utiliza un solo IC SLG47004

Figura 1: Oscilador de onda sinusoidal de puente de Wien básico

Nota 1: Algunos codificadores pueden tener uno de sus pines normalmente cerrado en estado estable. Esto hace que fluya corriente adicional a través de la resistencia pullup incluso cuando el dispositivo está apagado. En este caso, el consumo de corriente en estado apagado es de unos 9,5 uA, que también es despreciable.

Nota 2: El dispositivo no tiene un indicador de encendido. Se pueden usar transistores externos y LED de baja potencia para agregar si se desea.

FIGURA 2: CIRCUITO OSCILADOR DE ONDA CUADRADA/SIN SENUSO DE DOS RANGOS, AJUSTABLE, CONTROLADO POR CODIFICADOR

Tabla de contenido

operación de diseño

1. Diseño esquemático

Como se mencionó anteriormente, este diseño usa solo un chip. El SLG47004 IC empaqueta todas las macroceldas analógicas y digitales necesarias en un pequeño paquete STQFN-24 de 3 x 3 mm. Consulte la Figura 3 para ver el esquema completo. Diseñador GreenPAK plan.Archivos de diseño completos disponibles aquí.

Sección analógica

Este proyecto utiliza casi todas las macroceldas analógicas en el IC. La sección central reproduce OPAMP0, que es el oscilador en sí. El circuito representa un oscilador de onda sinusoidal de puente Wien muy modificado. El principal problema con el Wien Bridge Oscillator es la inestabilidad. La ganancia de OPAMP debería ser exactamente 2. De lo contrario, no comenzará a oscilar, o se sobrecargará y la onda sinusoidal de salida se distorsionará. Esto requiere el uso de resistencias de precisión (R1 y R2) para establecer la ganancia, e incluso entonces las variaciones de temperatura y voltaje asociadas con las imperfecciones de OPAMP pueden provocar oscilaciones inestables. Se ha agregado un circuito de recorte suave, R3D1D2, para solucionar este problema. Limita suavemente la ganancia y agrega estabilidad de temperatura sin distorsionar la forma de onda de salida.

Las resistencias variables digitales RH0 y RH1 se utilizan para ajustar la frecuencia. Su resistencia varía según un código digital del circuito de control, y los condensadores C1 y C2 (o C1+C3 y C2+C4) junto con las resistencias R4 y R5 establecen la frecuencia.

FIGURA 3: PROYECTO DE OSCILADOR DE ONDA SINusoidal/CUADRADA DE 2 RANGOS, AJUSTABLE, CONTROLADO POR CODIFICADOR

Los interruptores analógicos SWITCH0 y SWITCH1 son responsables de cambiar entre dos rangos de frecuencia. En estado apagado, los capacitores C3 y C4 están desconectados del circuito y el oscilador opera en el segundo rango (450 Hz a 43 kHz). Cuando el interruptor está en el estado ON, los condensadores C3 y C4 se conectan en paralelo con los condensadores C1 y C2. Esto hace que el oscilador trabaje en el primer rango de frecuencia (15 Hz a 1,4 kHz).

VREF OA0 se utiliza como referencia de tensión. Configure en VDD/2 y emita en PIN 20 a través del búfer HD/B.

OPAMP1 se configura como ACMP y se utiliza para convertir la onda sinusoidal generada en una onda cuadrada. También tiene su propio voltaje de referencia, que también se establece en VDD/2 y se conecta a la entrada inversora.

Parte digital

Todo el reloj para este diseño se realiza mediante un único oscilador de 2,048 kHz de baja potencia, OSC0. Esta es la única macrocélula que sigue funcionando cuando el dispositivo está apagado. No obstante, la corriente de reposo en estado desactivado es inferior a 1 uA, lo que permite que la batería se conecte directamente al chip sin el uso de un interruptor mecánico de encendido/apagado.

Este diseño utiliza varios contadores/retrasos. CNT3/DLY3 está configurado como un retraso de 23 ms y se usa como botón antirrebote. Controla los interruptores analógicos SWITCH0 y SWITCH1 junto con DFF13 y LUT1 (configurado como AND lógico). Por lo tanto, una sola pulsación breve del botón del codificador selecciona el rango de generación de frecuencia.

CNT4/DLY4 está configurado como detector de frecuencia con un período de 500 ms, por lo que reaccionará al menos a dos pulsaciones de botón en 500 ms. Junto con DFF14 y LUT0, activa/desactiva la salida de onda cuadrada.

CNT0/DLY0 está configurado como un retraso de 2 segundos y actúa como un interruptor de encendido junto con DFF17. Por lo tanto, al mantener presionado el botón del codificador durante más de 2 segundos, se encienden/apagan todas las macroceldas analógicas.

CNT1/DLY1 y CNT2/DLY2 están configurados como retrasos de 1,5 ms para actuar como antirrebote del codificador. CNT2/DLY2 y DFF12 actúan como detectores de dirección de rotación del codificador, obligando al contador del reóstato a contar hacia arriba o hacia abajo. Mientras tanto, ambas señales de reloj del reóstato pasan desde CNT1/DLY1 a través del detector de velocidad de rotación del codificador, que consta de CNT5/DLY5, LUT11, CNT6/DLY6 y LUT12.

CNT5/DLY5 está configurado como one-shot de 5 ms. Cada clic del codificador produce un solo pulso de aproximadamente 5 ms. Luego, estos pulsos se envían a las entradas IN2 e IN1 de LUT11 (configuradas como un AND lógico) y, al mismo tiempo, se envía un pulso de reloj (2.048 kHz) a la entrada IN3. Como resultado, se forma un paquete de 10 pulsos en su salida.

CNT6/DLY6 está configurado como detector de frecuencia con un período de 40 ms. Detecta la velocidad de rotación del codificador y emite 1 o 10 pulsos cada vez que el codificador hace clic en la entrada CLK de ambos reóstatos con la ayuda de un multiplexor (LUT12). Entonces, si el usuario gira el codificador lentamente, cada clic equivale a 1 pulso y equivale a 1 bit, lo que aumenta la resistencia actual del reóstato en aproximadamente 100 ohmios (dependiendo de la dirección de rotación) para una configuración o disminución precisa de la frecuencia. De lo contrario, si la velocidad de rotación es lo suficientemente alta, cada clic equivale a 10 pulsos y 10 bits, por lo que el reóstato cambia la resistencia en 10 pasos para un barrido de frecuencia rápido.

2. Rendimiento típico

Tabla 1. Características típicas a VDD = 4,5 V, T = 25 °C, sin carga

Figura 4: Primer rango, salida de onda sinusoidal, mínimo.frecuencia

Figura 5: Primer rango, salida de onda sinusoidal y onda cuadrada, mínimo.frecuencia

Figura 6: Primer rango, salida de onda sinusoidal y onda cuadrada, máx.frecuencia

Figura 7: Segundo Rango, Salida Sinusoidal, Mínimo.frecuencia

Figura 8: Segundo rango, salida de onda sinusoidal y onda cuadrada, mínimo.frecuencia

Figura 9: Segundo rango, salida de onda sinusoidal y onda cuadrada, máx.frecuencia

3. Configuración de macrocélulas

OSC0 configuración: Por defecto.

I2C configuración: Por defecto.

Tabla 2: Configuración de PIN

Tabla 3: Configuración de OPAMP

Tabla 4: Configuración de Vref

Tabla 5: Configuración del búfer HD

Tabla 6: Configuración del reóstato digital

TABLA 7: AJUSTES DEL INTERRUPTOR ANALÓGICO

Tabla 8: Configuración de LUT

Tabla 9: Configuración de DFF

Tabla 10: Configuración de CNT/DLY

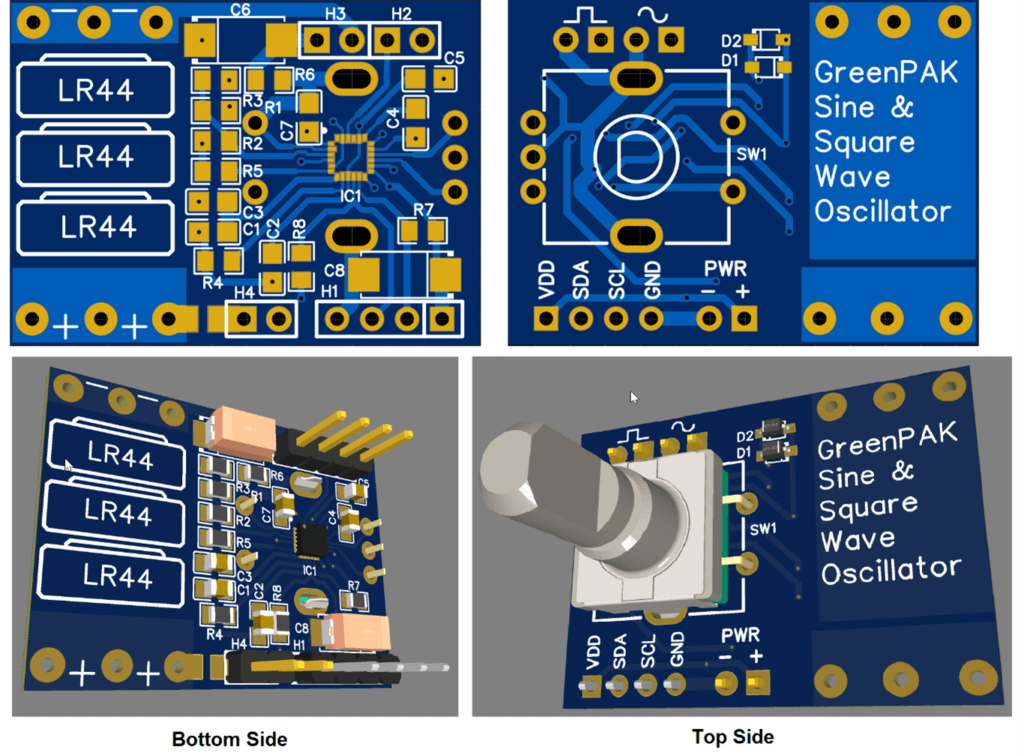

4. Diseño de PCB

Los PCB son easyeda.com servicio. Consulte las Figuras 10 y 11 para ver el esquema completo, el diseño de PCB y el modelo 3D de PCB. El tamaño del tablero es de 25 x 34 mm. La Figura 12 muestra una foto del prototipo.

FIGURA 10: ESQUEMA COMPLETO

Figura 11: diseño de PCB y modelo 3D

Figura 12: Foto prototipo

5. Software de simulación

GreenPAK Designer tiene la capacidad de simular su diseño. Para ello se diseñó un circuito simplificado (ver Figura 13). Los resultados de la simulación se muestran en las Figuras 14 y 15.

FIGURA 13: DISEÑO DE CIRCUITO SIMPLIFICADO

Figura 14: Resultados de la simulación. C1 = C2 = 3,3n

Figura 15: Resultados de la simulación. C1 = C2 = 100n

Conclusión

Como puede ver, es muy fácil diseñar y construir un oscilador de onda sinusoidal/cuadrada de dos rangos controlado por codificador ajustable utilizando OPAMP PAK. El SLG47004 resultó ser el IC perfecto para diseños que contienen todas las macroceldas analógicas y digitales necesarias. El diseño que se muestra en este documento es una de las muchas versiones de dispositivos que se pueden construir en base al SLG47004. Algunas macroceldas no utilizadas se pueden usar para diseñar funciones adicionales. Por el contrario, si no se necesita alguna funcionalidad, se puede eliminar fácilmente del diseño.