Esta nota de aplicación describe el chip TW2880P-BC2-GR. Este documento presenta Clockgen y PLL, incluidos los registros SCK, MCLK y VCLK. Se muestra el diseño de PCB del chip, incluido el diseño de SDRAM, DAC y HDMI. Este documento también cubre la decodificación, grabación y unidades SPOT de ventana PB e ID de canal, configuración de pantalla basada en TW2880C, OSG y OSD simple, detección de movimiento e interrupciones, capacidades DMA, interfaces de audio y diferencias entre C2 y C2. B1.

Sección 1: Clockgen y PLL

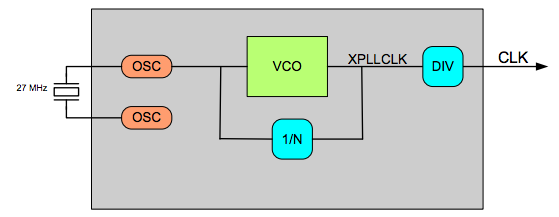

El TW2880C tiene tres dominios de reloj: dominio de reloj del sistema, dominio de reloj de memoria y dominio de reloj de video. Cada dominio de reloj admite diferentes tipos de unidades funcionales. Los relojes se generan a partir de tres PLL de ejecución libre diferentes. Después de la etapa VCO, el reloj de alta velocidad pasa por un divisor en serie y un selector de fase antes de llegar al circuito final. A continuación se muestra una descripción detallada de cada dominio de reloj.

SCLK

Se utiliza un reloj de sistema en todo el TW2880. La idea es usar también relojes que sean múltiplos de 27 en este grupo de relojes. La razón es clara. El reloj de 27 MHz es el reloj de datos del estándar BT.656. Debido a estas características, algunos decodificadores de video o secciones de salida CVBS utilizan este grupo de reloj.

lista de vigilancia

- Se generan 12 relojes a partir de este grupo de relojes.

- reloj del sistema de 108 MHz

- Sistemas de 54, 27 y 13,5 MHz para usar con bloques de E/S

- Reloj de sistema de 108 MHz con control de fase utilizado para la salida de grabación.

- Reloj escalador rápido de 216 MHz (432 MHz posible)

- Codificador de TV de doble monitor Reloj

- reloj de video de doble monitor

- Reloj de alta velocidad de doble monitor para escalador

- Reloj DAC de dos monitores

- Reloj de video externo de doble monitor para VGA

- Reloj de salida del puerto de red

Configuración del registro SPLL

En caso normal, [0x207] un poco[5:0] El valor predeterminado está diseñado para ser 5’d31 porque xpllclk es 864 MHz y al dividirlo por 8 circuitos se obtiene un reloj del sistema de 108 MHz.

[0x216] Utilice los bits 2, 3 y 4 para seleccionar la fase de los relojes de 108 MHz, 54 MHz y 27 MHz.

[0x216] Los bits 1,0 se utilizan para seleccionar la fase del reloj de 108 MHz. Esto ajusta la relación reloj/datos en el puerto de registro.

[0x21F] Los bits 2:1 se utilizan para seleccionar la fuente del reloj del monitor dual. Si se requiere CVBS, se debe usar un reloj generado a partir del grupo SCLK. Para los modos de visualización relevantes que no sean de 27 MHz, estos dos bits deben establecerse en 1 para usar un reloj generado a partir del grupo VCLK.