Esta nota de aplicación está destinada a ayudar a los usuarios a comprender cómo y cómo conectar los módulos LCD a los procesadores integrados de la serie EP93xx. Este artículo también incluye cómo determinar si su LCD es compatible con EP93xx.

Esta nota de aplicación está destinada a ayudar a los usuarios a comprender cómo y cómo conectar los módulos LCD a los procesadores integrados de la serie EP93xx. Este artículo también incluye cómo determinar si su LCD es compatible con EP93xx.

El propósito de este documento es ayudar a los usuarios a comprender cómo conectar un módulo LCD a la serie EP93xx de procesadores integrados de Cirrus Logic. Hay varios ajustes de temporización y salida disponibles para conectarse a muchas pantallas LCD monocromáticas y en color. Algunos modos de temporización también permiten la conexión a un DAC de video externo, que se puede usar para controlar cualquier tipo de pantalla.

Esta nota de aplicación se centra en el uso típico de un ejemplo específico de una pantalla LCD. Entonces, el ejemplo fue diseñado y probado con valores estándar para mostrar que se puede usar el controlador LCD. Cuando se utiliza el controlador LCD fuera de estos casos comunes, el usuario debe probar y validar la aplicación en el entorno de destino. Además, este documento no reemplaza la información en la Guía del usuario de EP93xx y el capítulo de la Guía del usuario de la hoja de datos de EP93xx “Raster Engine with Analog/LCD Integrated Timing and Interface” antes de usar esta nota de aplicación.

En este documento, las señales se identifican en figuras y ecuaciones por sus correspondientes nombres de señal EP93xx, a menos que se especifique lo contrario.

Cómo comprobar si la pantalla LCD es compatible con EP93xx

El motor de trama EP93xx es muy versátil y funciona con muchos tipos diferentes de pantallas LCD. Para determinar si su pantalla es compatible, siga estos pasos:

- Consulte el apéndice al final de este manual para ver si su pantalla se muestra como ejemplo. Si es así, use la configuración de registro especificada para esa pantalla. De lo contrario, vaya al paso 2.

- Examine la forma de onda. Si el tiempo de visualización que desea coincide con uno de estos diagramas (o difiere solo en la polaridad de la señal), la siguiente sección describe cómo configurar los registros de tiempo de trama del EP93xx. Si su pantalla no coincide con ninguno de estos, consulte Otros tipos de pantallas de datos de cuadros para obtener más información. Tenga en cuenta que las señales AC, XECL e YSCL no se ilustran en estos diagramas, pero se describen en la sección Temporización de video del capítulo Raster Engine de la Guía del usuario de EP93xx.

- Después de confirmar que el EP93xx puede generar una señal de sincronización, debe seleccionar el modo de salida de píxeles adecuado.

Si los requisitos de tiempo de su pantalla o el formato de entrada de píxeles no son compatibles, aún puede admitir la pantalla usando pines GPIO para generar los tiempos apropiados. Sin embargo, esto consume más tiempo de procesador, pero puede ser una opción viable en pantallas más lentas/pequeñas. Debido a la versatilidad del motor de trama EP93xx, intentamos cubrir los tipos de pantallas más comunes. Tenga en cuenta que si bien se ha tenido cuidado en el diseño de este bloque, no todos los paneles LCD son compatibles.

Generación de reloj de video VidClk

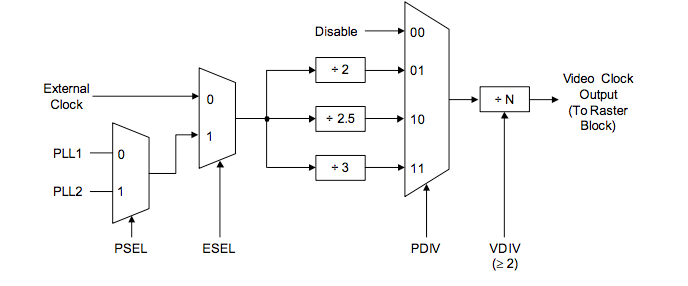

El reloj de video interno (VIDCLK) que impulsa el motor de trama y el reloj de píxeles externo (SPCLK) pueden provenir de PLL1, PLL2 o una entrada de reloj externa. La señal SPCLK registra los datos del EP93xx en una pantalla o pantalla LCD externa. El número de píxeles por SPCLK puede ser 1, 2, 4, 8 o 2-2/3.

Conceptualmente, el reloj externo (SPCLK) se genera dividiendo VIDCLK por el reloj dividido apropiado. El divisor requerido depende del modo de salida. 1 píxel por SPCLK da como resultado 1 VIDCLK por SPCLK. Con 4 píxeles por SPCLK, hay 4 VIDCLK por SPCLK. Tenga en cuenta que el modo 2-2/3 es un caso especial en el que el primer SPCLK tiene tres VIDCLK, el segundo SPCLK tiene 2 y el tercero SPCLK tiene 3. Este patrón se repite cada 8 píxeles (es decir, 8 VIDCLK).

VIDCLK se obtiene dividiendo la fuente de reloj (PLL!, PLL2 o reloj externo) por el prescaler y dividiendo por N bloques de divisores donde N ≥ 2. Esto se muestra en el diagrama de bloques de la Figura 1. Los valores de PSEL, ESEL, PDIV y VDIV son todos campos de bits en el registro VidClkDiv en el controlador del sistema. Consulte la Guía del usuario de EP93xx (sección Controlador del sistema) para obtener más información sobre el registro VidClkDiv.