Por Jean-Marie Brunet, director sénior de marketing, división de emulación

Mentor, negocio de Siemens

www.mentor.com

En noviembre, Apple anunció su primer diseño de sistema en chip (SoC) de 16 000 millones de transistores como parte de una familia de SoC que se fabricará en el nodo de proceso de 5 nm.

Cuando se mide en puertas equivalentes a ASIC, el nuevo Apple SoC equivale a alrededor de 4 mil millones de puertas. Aunque enorme, no es el chip semiconductor más grande del mercado. Algunos de los diseños SoC más grandes de la actualidad alcanzan más de 10 mil millones de puertas.

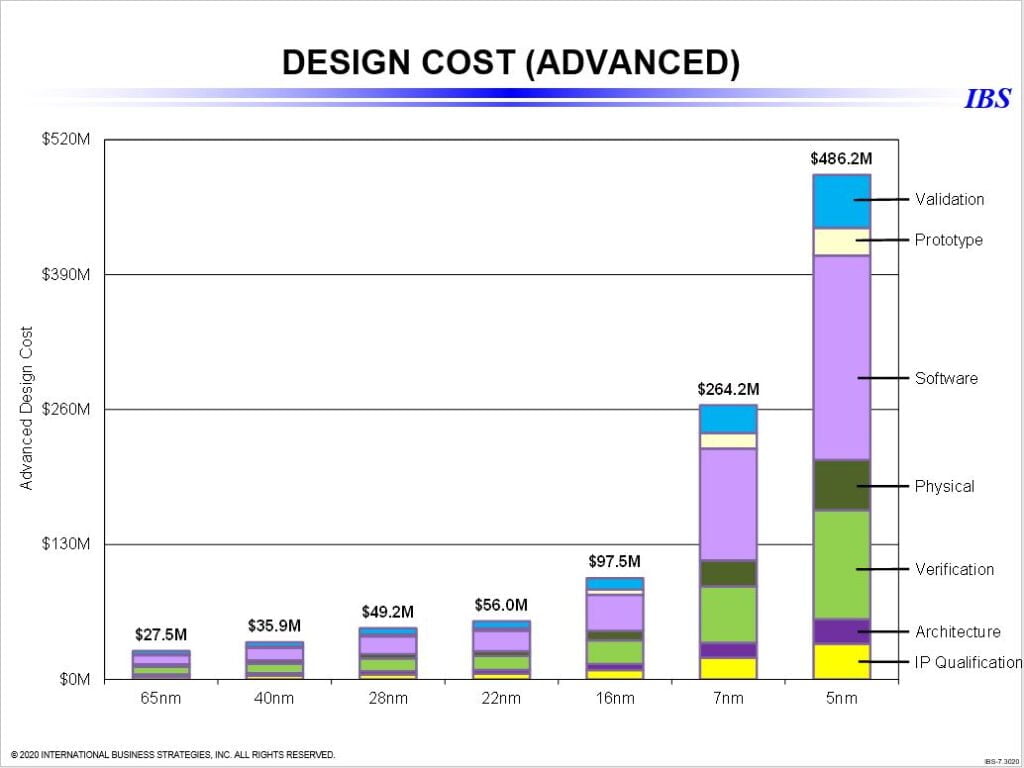

Aún así, la complejidad medida por el recuento de transistores o el recuento de puertas solo captura la dimensión de hardware de la complejidad del diseño. Otro aspecto, el software, es considerado por algunos como un aspecto aún más importante que el hardware. El siguiente gráfico muestra los costos de verificación y verificación de hardware y software en cada nodo de tecnología de proceso, lo que demuestra el papel dominante del software de 65 nm a 5 nm.

A 28 nm, el costo de la verificación del software ha superado el esfuerzo de verificación del hardware. (Fuente: SII)

No hace falta decir que diseñar y validar los diseños de SoC actuales es una tarea abrumadora. Siempre es más fácil crear un diseño más grande porque tiene acceso a un mayor nivel de abstracción que validar el mismo diseño.

La respuesta a esta demarcación es un enfoque de verificación doble en el que la simulación RTL se complementa con la verificación asistida por hardware en el nivel completo de SoC.

Las simulaciones de software utilizadas a nivel de subsistema deben extenderse a nivel de sistema mediante el uso de cargas de trabajo reales y puntos de referencia para facilitar la verificación. Esto es especialmente importante al verificar los aspectos de potencia y rendimiento de su diseño. Un punto interesante a tener en cuenta es que la carga de trabajo real y el uso de referencia varían según el segmento de mercado objetivo.

Por ejemplo, AnTuTu, Geekbench y GFXBench se usan en el mercado móvil, mientras que Car Chase y Manhattan se usan en el mercado de gráficos.

En función de estas cargas de trabajo, se requiere una plataforma de verificación asistida por hardware que incluya emulación y creación de prototipos FGPA implementada en modo virtual para ejecutar el diseño bajo prueba (DUT) en estas cargas de trabajo. Es importante contar con un entorno virtual para esta validación. Esto se debe a que proporciona un entorno determinista, iterativo en lugar de aleatorio para encontrar errores de diseño.

Para cumplir con los requisitos, una plataforma de verificación asistida por hardware debe:

- Ofrece una capacidad masiva y escalable de más de 10 000 millones de puertas

- Mantenga una comunicación de gran ancho de banda con los servidores host para manejar las cargas de trabajo y los puntos de referencia del mundo real

- Visibilidad completa del dispositivo bajo prueba en tiempo de ejecución

Las herramientas de creación de prototipos de FPGA deben servir como complemento de los emuladores de hardware como parte de una plataforma de verificación asistida por hardware de alto rendimiento. Esto significa que las dos herramientas deben optimizar las ventajas y desventajas de la verificación para utilizar el ciclo de verificación de manera más eficaz. La elección entre los emuladores de hardware y los sistemas de creación de prototipos de FPGA se basa en la necesidad de una depuración precisa y la capacidad de realizar la verificación del software y del sistema rápidamente.

Como muestra el anuncio de Apple, la industria de semiconductores y sistemas continúa evolucionando rápidamente. Las aplicaciones emergentes como AI/ML, 5G/6G y la conducción autónoma están redefiniendo el uso de la simulación de software y las plataformas de verificación asistida por hardware.

Jean-Marie Brunet es director sénior de marketing de la división de emulación de Mentor, una empresa de Siemens. Tiene más de 20 años de experiencia en funciones de ingeniería de aplicaciones, marketing y gestión en la industria de EDA, incluidos puestos de gestión de diseño y diseño de circuitos integrados en STMicrolectronics, Cadence y Micron. Brunet tiene una Maestría en Ciencias en Ingeniería Eléctrica de la Escuela de Ingeniería Electrónica ISEN en Lille, Francia.