descripción general

Esta nota de aplicación describe el convertidor de analógico a digital (ADC) ISLA11xP50. El propósito de este documento técnico es proporcionar información básica sobre los procedimientos de sincronización y temporización de datos de salida de ISLA11xP50.

La captura de datos del ISLA11xP50 ADC es fácil con la tecnología FPGA actual. Una interfaz LVDS síncrona de fuente proporciona datos de salida DDR de hasta 500 MHz con un reloj de 250 MHz. El reloj y los datos se regulan dentro de ± 250ps, lo que proporciona un área válida de datos amplia garantizada de 1,5 ns sobre el proceso, el voltaje y la temperatura a una operación de 500 MSPS.

Internamente, el reloj de entrada se divide inmediatamente por 2 para sincronizar los dos núcleos ADC a la mitad de la frecuencia de muestreo de salida. El flujo de datos de salida de 500 MSPS es producido por dos núcleos ADC intercalados, pero los datos de salida siempre se entregan en una secuencia conocida desde un ISLA11xP50. Múltiples ADC con alineación de borde de reloj de entrada pueden no tener alineación de borde de reloj de salida debido a la incertidumbre de la fase de salida dividida por 2. La señal CLKOUTP puede subir o bajar en el flanco ascendente del reloj de entrada, a menos que se fuerce específicamente a un estado conocido.

El ISLA11xP50 incluye una función de sincronización para facilitar el diseño de sistemas que requieren muestreo simultáneo o incluso intercalado. La sincronización es tan fácil como usar un solo reloj de datos de salida ADC o el pin CLKDIVRST para forzar la sincronización. Un enfoque más complejo podría usar el registro PHASE_SLIP para ajustar el tiempo. El mejor método depende de muchos factores, incluidos los márgenes de tiempo, la familia de FPGA, las herramientas de diseño de FPGA y las restricciones de la placa de circuito impreso (PCB). Con una operación de 500 MSPS, la configuración de CLKDIVRSTP y el tiempo de retención pueden ser un desafío en algunos diseños. Estos requisitos de temporización se pueden relajar de manera efectiva activando el reloj de entrada del ADC para proporcionar un margen adicional.

temporización de salida

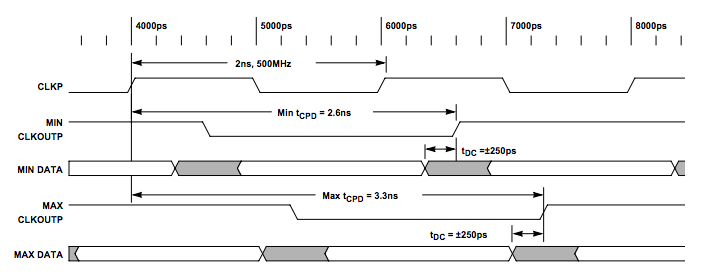

El reloj de entrada y los datos del ISLA11xP50 se propagan a través del ISLA11xP50 en rutas de retardo similares para facilitar los requisitos de tiempo de captura de datos. Los DATOS de salida del ADC pasan de una muestra a la siguiente dentro de ±250ps de la señal CLKOUTP. Deje una amplia ventana válida de datos de 1,5 ns a 500 MSPS. CLKOUTP retrasa a CLKP entre 2,6 ns y 3,3 ns a 1,8 V y +25 °C, como se muestra en la Figura 1. O -40°C a +85°C.

Funcionamiento interno

El funcionamiento intercalado del ISLA11xP50 requiere que el reloj de entrada de 500 MHz se divida por 2 para que cada núcleo muestree a 250 MSPS. La Figura 2 muestra un diagrama conceptual del circuito de reloj interno del ADC. La fase del reloj de salida (CLK_A, CLK_B en la Figura 2) es indeterminada porque el divisor de reloj generalmente se activa desde el reinicio de encendido en un estado aleatorio. En funcionamiento normal con un solo ADC, la fase de reloj desconocida no importa y el orden de las muestras de salida siempre es correcto. Este puede no ser el caso cuando se sincronizan varios ADC. La incertidumbre de fase de CLKOUTP significa que los flancos ascendentes de CLKOUTP pueden no estar alineados en múltiples ADC controlados por la misma fuente de reloj. Como se muestra en la Figura 3, esta posible diferencia de fase puede generar diferencias inesperadas en el tiempo de muestra y la secuencia de los datos capturados.

Sincronización

ISLA11xP50 proporciona dos mecanismos para controlar la fase del reloj de salida.

- El pin CLKDIVRSTP proporciona la forma más fácil de sincronizar múltiples ADC. Si CLKDIVRSTP se establece alto dentro de los tiempos de configuración y espera en la hoja de datos, la señal CLKOUTP siempre será forzada a una fase conocida. Al enrutar CLKP y CLKDIVRSTP a múltiples ADC con retardos de PCB iguales, todos los ADC se pueden configurar en la misma fase de muestra al mismo tiempo. La afirmación de CLKDIVRSTP puede hacer que la DLL interna pierda el bloqueo hasta por 52 µs. Se pueden obtener datos válidos después de este período de 52 µs. Este proceso debe completarse después de cada ciclo de encendido o reinicio del ADC.

- Escribir en el registro PHASE_SLIP (0x71) invierte efectivamente la señal CLKOUTP. El modo de prueba de usuario puede generar pares de valores conocidos, pero usar estos valores para determinar la relación de fase del reloj requiere más código FPGA que usar CLKDIVRSTP. Después de sincronizar con CLKDIVRSTP, el registro PHASE_SLIP se puede usar para retrasar los datos de salida para intercalar aún más varios ADC.

Si necesita relajar la configuración de CLKDIVRSTP y los tiempos de espera, puede desactivar el reloj de entrada, establecer CLKDIVRSTP alto y luego volver a habilitar el reloj. Se debe utilizar un circuito de activación de reloj sin fallas para garantizar un funcionamiento confiable.