Esta nota de aplicación describe cómo implementar un bus maestro 1-Wire® utilizando un UART de microprocesador. Incluye una descripción de las interfaces eléctricas requeridas, la configuración de UART y las relaciones de temporización entre UART y las señales de 1 cable. La flexibilidad proporcionada en la configuración de temporización de bytes de UART facilita la implementación de intervalos de tiempo de 1 cable y pulsos de detección de presencia y reinicio. Al incorporar FIFO de transmisión y recepción profundas, se pueden transferir múltiples valores de byte a través del bus de 1 cable desde el procesador principal en solo unos pocos ciclos de reloj por bit requerido.

prólogo

Los dispositivos de 1 cable ofrecen soluciones económicas para identificación, memoria, temporización, medición y control. La interfaz de datos de 1 cable se reduce al mínimo absoluto: una línea de datos y una referencia de tierra. La mayoría de los dispositivos de 1 cable proporcionan cantidades de datos relativamente pequeñas, por lo que una velocidad de datos típica de 16 kbps es más que adecuada para su tarea. A menudo es útil usar los pines de entrada/salida de uso general (GPIO) de un microcontrolador de 8 o 16 bits en una forma de “golpe de bits” para actuar como un maestro de bus.

Sin embargo, en los sistemas de 32 bits, las frecuencias de reloj del procesador normalmente superan los 100 MHz, y el uso de un pin GPIO como maestro de bus de 1 cable consume una gran cantidad de ciclos de reloj por bit de 1 cable. Los sistemas portátiles de 32 bits consumen una valiosa energía de la batería mientras cronometran los intervalos de tiempo de lectura y escritura de 1 cable. Algunos sistemas descargan la carga de las operaciones de sincronización de bits y tramas de bytes del procesador principal. DS1WM Un bloque de hardware de 1-Wire Bus Master* sintetizable dentro del conjunto de chips.si DS1WM O, si no hay otro puerto maestro de hardware de 1 cable disponible, hay disponible un canal de transmisor receptor asíncrono universal (UART) para facilitar la comunicación con dispositivos de 1 cable.

Esta nota de aplicación incluye una descripción de las interfaces eléctricas requeridas, la configuración de UART y las relaciones de temporización entre UART y las señales de 1 cable. Se asume una comprensión general de la comunicación de 1 cable. Los tiempos estándar y los niveles lógicos se utilizan en las siguientes descripciones. Los lectores deben consultar la hoja de datos específica del dispositivo de 1 cable para conocer las especificaciones y tolerancias específicas de tiempo y voltaje.

resumen conceptual

Un UART con capacidad para 115 200 bit/s, configurado correctamente para la velocidad en baudios, la cantidad de bits de datos por carácter, la paridad y la cantidad de bits de parada, proporciona los tiempos de entrada y salida necesarios para implementar un maestro de 1 cable. El UART genera pulsos de reinicio de 1 cable y ranuras de tiempo de lectura y escritura. El microprocesador transmite un bit 1 o 0 en el 1-Wire simplemente colocando un código de carácter de 1 byte en el registro de transmisión UART y el UART hace el trabajo. Por el contrario, el microprocesador lee códigos de caracteres de un solo byte correspondientes a 1 o 0 bits leídos desde el esclavo de 1 cable. Todas las transferencias de bits de 1 cable requieren que el bus maestro, el UART, lleve el bus de 1 cable a nivel bajo para iniciar el ciclo. Por lo tanto, cada ciclo de bits de 1 cable incluye un envío de bytes y una recepción de bytes por parte del UART. Para las lecturas, los datos recibidos son importantes, pero para las escrituras, los bytes recibidos se descartan. Dependiendo de la profundidad de los búferes de lectura y escritura del UART, primero en entrar, primero en salir (FIFO), el UART también puede enmarcar los bits de 1 cable en valores de bytes para reducir aún más la sobrecarga del procesador.

Interfaz eléctrica de UART a 1-Wire

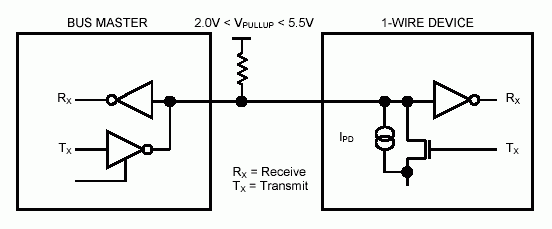

Los dispositivos de 1 cable funcionan en un entorno de drenaje abierto con voltajes de bus que oscilan entre 2,0 V y 5,5 V. El nivel lógico exacto y el voltaje pull-up mínimo dependen del dispositivo, pero los dispositivos alimentados por parásitos generalmente requieren un voltaje pull-up de 2,8 V para recargar un capacitor de almacenamiento interno que se usa para alimentar períodos cuando la línea de datos es baja. se requiere. Una resistencia de 4,7 kΩ normalmente actúa como pull-up para la línea de datos de 1 cable. La resistencia proporciona pasivamente una señal lógica alta mientras que el bus maestro y todos los dispositivos esclavos manejan señales lógicas bajas. Los dispositivos suelen contener un menú desplegable interno débil, que se muestra como Ipd en la Figura 1.

La mayoría de los pines de transmisión de datos UART (TXD) no son de drenaje abierto, por lo que generalmente se requiere un circuito de búfer de drenaje abierto externo. Este circuito se puede construir a partir de componentes discretos, como se muestra en la Figura 2, o a partir de una solución integrada como Fairchild. NC7WZ07 Disponible como se muestra en la Figura 3. En ambos circuitos, una resistencia pull-up de 4,7 kΩ proporciona una lógica alta al bus de 1 cable.