Este documento contiene instrucciones para implementar serializador/deserializador o interfaces basadas en SerDes en la familia KeyStone I de dispositivos DSP. Estos incluyen Serial RapidIO (SRIO), Antenna Interface (AIF), HyperLink, Serial Gigabit Media Independent Interface (SGMII), interfaz Peripheral Component Interconnect Express (PCIe).

Este documento contiene instrucciones para implementar serializador/deserializador o interfaces basadas en SerDes en la familia KeyStone I de dispositivos DSP. Éstas incluyen:

- Serie RapidIO (SRIO)

- Interfaz de antena (AIF)

- Hipervínculo.

- Interfaz Serial Gigabit Media Independent Interface (SGMII)

- Interconexión de componentes periféricos Express (PCIe)

Serial RapidIO es una interconexión de paquetes conmutados de alta velocidad estándar de la industria. La interfaz de la antena es compatible con dos estándares de la industria para soluciones de estaciones base celulares. Estos son la Iniciativa de Arquitectura de Estación Base Abierta (OBSAI) y la Interfaz de Radio Pública Común (CPRI). SGMII es el estándar utilizado para conexiones Gigabit Ethernet de MAC a MAC o de MAC a PHY. Peripheral Component Interconnect Express (PCIe) es una interconexión serial de alta velocidad. HyperLink es la interconexión basada en paquetes de alta velocidad de Texas Instruments.

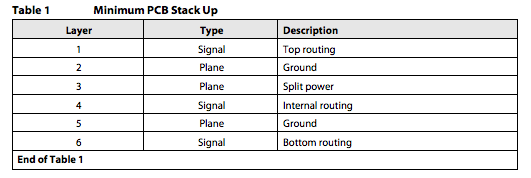

Para cada una de estas interfaces, la transmisión de datos de la capa física utiliza SerDes analógicos para alimentar búferes lógicos de modo de corriente diferencial (CML) de baja oscilación de salida. El diseño adecuado de la placa de circuito impreso (PCB) para estas interfaces se parece al diseño analógico o de RF y es muy diferente del diseño de bus digital paralelo tradicional.

Debido a la naturaleza analógica de esta interfaz basada en SerDes, no es posible especificar la interfaz de la forma tradicional de interfaz digital DSP. Además, no es deseable especificar las interfaces en términos de requisitos físicos brutos establecidos por las especificaciones estándar de la industria. Comprender estas especificaciones y crear PCB que cumplan con los requisitos explícitos e implícitos requiere mucho tiempo, experiencia y herramientas costosas.

Para las interfaces basadas en KeyStone I SerDes, el enfoque es reducir la especificación a un conjunto de reglas de enrutamiento de PCB y configuraciones del sistema fáciles de entender. TI ha realizado trabajos de simulación y diseño de sistemas para garantizar que se cumplan los requisitos de interfaz adecuados. Este documento proporciona pautas que darán como resultado una implementación a nivel de placa que cumpla con los requisitos de la interfaz.