Esta nota de aplicación presenta un ejemplo de configuración para la transmisión y recepción de Ethernet/IEEE 802.3 utilizando el controlador Ethernet V850E2/ML4. Describe las especificaciones de ejemplo de aplicación, las funciones utilizadas, las condiciones, la inicialización, la negociación automática de PHY IC, la configuración de transmisión/recepción y la asignación de selección de programa de muestra utilizada en los ejemplos de aplicación.

Esta nota de aplicación presenta un ejemplo de configuración para la transmisión y recepción de Ethernet/IEEE 802.3 utilizando el controlador Ethernet V850E2/ML4. Describe las especificaciones de ejemplo de aplicación, las funciones utilizadas, las condiciones, la inicialización, la negociación automática de PHY IC, la configuración de transmisión/recepción y la asignación de selección de programa de muestra utilizada en los ejemplos de aplicación.

especificación

- Este programa de muestra no incluye el manejo de errores de envío/recepción. El usuario debe implementar este manejo de errores si es necesario.

- Después de liberar reset, el programa de ejemplo establece el bus H, los registros de E/S y los temporizadores.

- LAN8700i de Standard Microsystems Corporation se utiliza como Ethernet PHY IC.

- El enlace Ethernet PHY IC adopta la función de negociación automática.

- En el programa de ejemplo, se pueden seleccionar los siguientes dos tipos de procesamiento.

Inicialización

Para usar el controlador Ethernet incluido en el código de muestra, necesita un programa de inicialización para inicializar hardware como el bus H. En esta sección se describen los ajustes utilizados en el programa de muestra.

Programa de inicialización

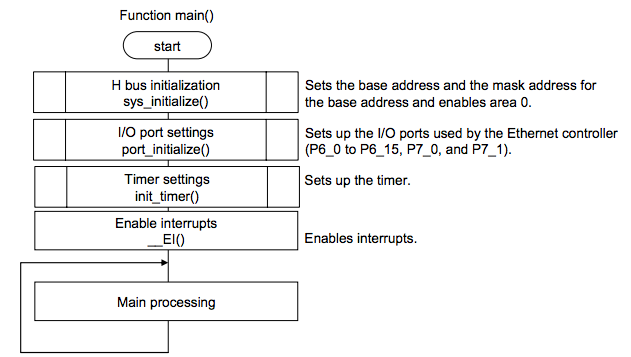

Después de que se libera el reinicio, lo primero que hace el programa principal es configurar el bus H, el puerto utilizado para Ethernet, el temporizador (TAUA0) y habilitar las interrupciones. La figura 1 muestra un diagrama de flujo de este proceso de inicialización.

Negociación automática de PHY IC

El programa de ejemplo utiliza la función de negociación automática proporcionada por Ethernet PHY IC. Los resultados de la negociación automática se leen del registro de lectura de PIN de puerto (PPR7).

Descripción general de las funciones que se utilizarán

El Ethernet PHY IC realiza el procesamiento de enlace de capa física. Esto permite que el controlador Ethernet integrado V850E2/ML4 obtenga el resultado del enlace simplemente leyendo el resultado del enlace del Ethernet PHY IC. El programa de muestra habilita la función de negociación automática proporcionada por PHY IC.

La interfaz entre el controlador Ethernet y Ethernet PHY IC cumple con los estándares IEEE 802.3 MII (interfaz independiente de medios) y RMII (interfaz independiente de medios reducidos).

Los resultados de la negociación automática se almacenan en los registros internos de Ethernet PHY IC y se leen mediante la interfaz serial (interfaz de administración serial) usando los pines MDC y MDIO. El V850E2/ML4 puede leer y escribir estos pines mediante control de puerto.

Procedimiento de Acceso al Registro MII/RMII

Esta sección describe el procedimiento para acceder a los registros MII/RMII, que son registros internos de Ethernet PHY IC.

La interfaz serial (interfaz de administración serial) utilizada para acceder a los registros MII/RMII consta de dos pines: el pin MDC y el pin MDIO (ambos pines del controlador Ethernet). MDC es el pin de reloj síncrono y MDIO es el pin de E/S de datos. El estado de estos pines se puede ver y cambiar mediante el control de puertos. Los datos que se ajusten al formato prescrito (trama de gestión MII/RMII) deben salir en MII. En el programa de ejemplo, se emite Z0 de 1 bit en el estado IDLE. El estándar IEEE 802.3 no menciona entradas de reloj, pero algunos PHY IC no los conectan correctamente y esto se hace por seguridad.