En este artículo, exploraremos la lógica programable para acelerar los diseños basados en microcontroladores. Este artículo analiza brevemente los conceptos básicos de la lógica programable, la arquitectura FPGA, la tecnología de implementación de FPGA, los núcleos de procesador, los beneficios de los SoC y la flexibilidad de los procesadores en la electrónica automotriz.

Las capacidades de los dispositivos lógicos programables a gran escala, como las matrices de compuertas programables en campo (FPGA) y los dispositivos lógicos programables complejos (CPLD), han existido desde su primera introducción hace décadas como reemplazos de la lógica de unión y como dispositivos de creación de prototipos ASIC, está creciendo rápidamente. . Los aceleradores y microprocesadores integrados son fuertes candidatos para muchas aplicaciones que alguna vez se consideraron dominio exclusivo de DSP y ASSP. Una comprensión básica de las arquitecturas FPGA y CPLD puede mejorar el rendimiento, la eficiencia y el ciclo de diseño de muchos diseños.

La lógica programable tiene una larga historia de desarrollo antes de alcanzar sus formas más avanzadas en FPGA y CPLD. La diferencia arquitectónica entre las dos tecnologías está indicada por el propio nombre. Los FPGA tienen una estructura muy similar a los ASIC Gate Array y, de hecho, se usaron originalmente para la creación de prototipos de ASIC. Un CPLD es una red de elementos lógicos programables conectados para crear un sistema más grande.

Fundamentos de la lógica programable

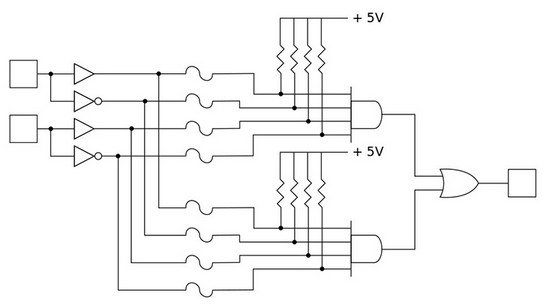

La idea de configuraciones básicas de FPGA y CPLD se puede entender rápidamente al revisar las características de la lógica de matriz programable (PAL). PAL comienza con un amplio plano AND programable para aplicar AND a las entradas. El plano OR es fijo, lo que limita el número de términos que se pueden combinar con OR. Agrega dispositivos lógicos básicos como multiplexores, OR exclusivos y pestillos, y también incluye elementos de reloj como flip-flops.

Esta combinación de elementos de circuito permite a los diseñadores implementar numerosas funciones lógicas, incluida la lógica secuencial sincronizada necesaria para las máquinas de estado. PAL es un dispositivo muy rápido y ha reemplazado gran parte de la lógica estándar en los diseños de generaciones anteriores. La Figura 1 muestra un PAL básico donde un elemento programable (que se muestra como un fusible) conecta las entradas verdadera y complementaria a una puerta AND. Las compuertas AND, también conocidas como términos de productos, se combinan para formar una matriz lógica de suma de productos.

Los CPLD y los FPGA crean un medio altamente escalable y satisfactorio entre los arreglos de puertas PAL y ASIC. CPLD es tan rápido como PAL pero más complejo. Los FPGA abordan la complejidad de los arreglos de puertas y son programables.

arquitectura CPLD

Cada proveedor de CPLD tiene su propia implementación, pero todos los CPLD tienen una característica común: consisten en bloques de funciones (FB), bloques de entrada/salida (E/S) y una matriz de interconexión. Los CPLD se programan utilizando elementos específicos de la tecnología del fabricante. Los dispositivos de memoria pueden ser celdas EPROM, celdas EEPROM o celdas Flash EPROM. La Figura 2 muestra la arquitectura de un CPLD típico.

arquitectura FPGA

Las arquitecturas FPGA son similares a las ASIC, pero completamente diferentes a las CPLD. Una arquitectura FPGA típica consta de un conjunto de bloques lógicos configurables (CLB), pads de E/S e interconexiones programables, como se muestra en la Figura 3. Se agrega un circuito de reloj para conducir la señal de reloj a cada bloque lógico. Las unidades aritméticas lógicas, las memorias y los decodificadores también son elementos típicos.

La lógica FPGA está contenida en CLB que contienen RAM que se utilizan para crear funciones lógicas combinatorias, también conocidas como tablas de búsqueda (LUT). También contiene flip-flops para elementos de almacenamiento de reloj y multiplexores para enrutar lógica dentro del bloque y entre recursos externos. Los multiplexores también se utilizan para la selección de polaridad, reinicio y selección de entrada clara.

Tecnología de implementación de FPGA

Los FPGA se han descrito tradicionalmente de acuerdo con la tecnología de memoria utilizada para almacenar la configuración lógica del FPGA. Hay cuatro actualmente en uso: FPGA basadas en SRAM, SRAM con memoria flash interna, basadas en flash y anti-fuse (también conocidas como OTP porque son programables una sola vez), cada una con sus propias fortalezas y debilidades.

Los FPGA basados en SRAM almacenan configuraciones de celdas lógicas en memoria estática organizadas como una matriz de pestillos. Dado que SRAM es volátil, este tipo de FPGA debe programarse cada vez que se inicia el sistema. Hay dos modos básicos de programación.

- modo maestro. Esto es cuando la FPGA lee los datos de configuración de una fuente externa, como un chip de memoria flash externo.

- En modo esclavo, la FPGA está configurada por un dispositivo maestro externo, como un procesador. Normalmente, esto se realiza mediante una interfaz de configuración dedicada o una interfaz de exploración de límites (JTAG).

- Los FPGA basados en SRAM con memoria flash interna contienen bloques de memoria flash interna que no requieren memoria no volátil externa.

- Los FPGA basados en True Flash utilizan flash como recurso principal para el almacenamiento de configuración, lo que elimina la necesidad de una memoria externa no volátil. Esta tecnología consume menos energía y es más tolerante a los efectos de la radiación que los FPGA basados en SRAM.

- Los FPGA basados en antifusibles (OTP) difieren de las tecnologías mencionadas anteriormente porque solo se pueden programar una vez. (Los dispositivos antifusible inicialmente no conducen corriente, pero pueden quemarse hasta un estado conductor).

núcleo del procesador

Los dispositivos programables se desarrollaron originalmente como una alternativa a la lógica de pegamento, pero a medida que aumentaba la densidad de las puertas, los proveedores de FPGA y CPLD comenzaron a agregar circuitos con funciones dedicadas para complementar las puertas no asignadas y las funciones lógicas del campo de arroz. El resultado se denomina sistema en chip programable (SoPC), donde un sistema completo de dispositivos complejos, como procesadores, se integra en un único dispositivo lógico programable.

La mayoría de los proveedores de FPGA y CPLD ofrecen familias de productos que brindan la funcionalidad de MCU y otros núcleos de IP. El núcleo brinda a los diseñadores de sistemas acceso a un rendimiento seleccionable para sus conjuntos de herramientas de desarrollo, sistemas operativos y aplicaciones familiares.

Beneficios de los SoPC

Hay varias razones convincentes para considerar el uso de un SoPC que contenga la funcionalidad de MCU. El primero es reconocer los costos ocultos de usar una MCU dedicada. Por ejemplo, si una parte no tiene la combinación correcta de funciones, se debe desarrollar una lógica externa y un software para llenar los vacíos funcionales. Los proveedores de MCU ofrecen dispositivos con funciones especializadas adaptadas a aplicaciones específicas, pero estos chips responden, por ejemplo, a las condiciones dinámicas del mercado que requieren nuevas interfaces y periféricos muy rápidamente.

Ejemplo: flexibilidad del procesador para electrónica automotriz

Los automóviles tienen un apetito infinito por MCU integrados. Todos los sistemas principales, como el control del motor, los frenos, el chasis, el entretenimiento, etc., tienen al menos un sistema. Tradicionalmente, esta demanda se ha satisfecho con MCU específicas de la aplicación, pero a medida que crece la cantidad de aplicaciones (y variantes de MCU), esta estrategia se cuestiona. Los fabricantes de automóviles buscan soluciones más flexibles y personalizables y, en algunos casos, los FPGA son la respuesta.