prólogo

Uno de los desafíos a los que se enfrentan con frecuencia los diseñadores digitales es eliminar los defectos de diseño. Esto generalmente se tiene en cuenta al garantizar una configuración adecuada y tiempos de espera cuando los datos están bloqueados.

Un “fallo” es una señal que no está activa durante un período de reloj. Si una señal con fallas alimenta las líneas de reloj de muchos latches, algunos latches pueden actualizarse y otros no. Claramente, esta es una situación que los diseñadores quieren evitar. También tenga en cuenta que el retraso de la propagación varía con la temperatura, por lo que un diseño que no genera fallas durante el desarrollo aún puede generar fallas en diversas condiciones.

Al agregar una celda lógica configurable (CLC) al conjunto de periféricos de Microchip, los usuarios finales pueden esencialmente “diseñar” un periférico simple que puede interactuar con un microcontrolador PIC. Dado que el dispositivo PIC tiene la capacidad de generar señales que provocan interrupciones e incrementan los contadores, es necesario proporcionar algunas instrucciones para que se pueda crear un diseño estable utilizando el periférico CLC.

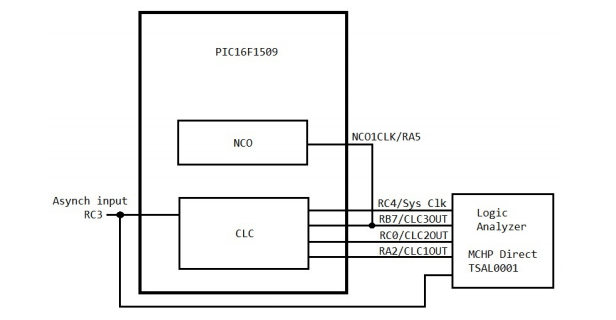

En este ejemplo se usa un PIC16F1509 y se usan 3 de los 4 módulos CLC disponibles. Se utiliza un cuarto módulo CLC para enrutar la señal FOSC interna al pin RC4 para que pueda verse con un analizador lógico. Otras señales dentro del CLC (salida XOR, salida de bloqueo) se envían a pines externos para brindar una imagen más clara de cómo funciona la aplicación.

El diagrama de bloques (Figura 1) muestra la señal de entrada asíncrona de RC3 con la salida CLC alimentando el analizador lógico. La señal CLC3 es una señal de reloj sin fallos y se proporciona en el pad NCO1CLK.

Este ejemplo crea un contador de alta velocidad que se usa para incrementar el registro NCO. El NCO aumentará mientras la señal de pulso externa sea alta. Dado que el contador NCO es un registro de 20 bits de ancho, esto crea un contador de larga duración de alta resolución. Se necesitan aproximadamente 16 ciclos de instrucción (4 µs con un reloj de 16 MHz) para leer los datos y restablecer el contador, por lo que debe haber al menos 4 µs de tiempo bajo entre pulsos. Un indicador de interrupción de flanco descendente en CLC2 proporciona una señal de que la medición del ancho de pulso está completa. Aunque los registros NCO están diseñados para ser tolerantes a fallas en la entrada del reloj, aún es una buena práctica de diseño proporcionar una señal limpia a la línea de reloj NCO.

El diseño inicial de este circuito permite que pasen los fallos. Este es un simple “Y” de la señal de pulso y el reloj del sistema. Tenga en cuenta que el reloj se dispara cuando la señal del pulso sube justo antes de que el reloj caiga (Figura 2).