Las capacidades de los dispositivos lógicos programables a gran escala, como las matrices de compuertas programables en campo (FPGA) y los dispositivos lógicos programables complejos (CPLD), han existido desde su primera introducción hace décadas como reemplazos de la lógica de unión y como dispositivos de creación de prototipos ASIC, está creciendo rápidamente. . Los aceleradores y microprocesadores integrados son fuertes candidatos para muchas aplicaciones que alguna vez se consideraron dominio exclusivo de DSP y ASSP. Una comprensión básica de las arquitecturas FPGA y CPLD puede mejorar el rendimiento, la eficiencia y el ciclo de diseño de muchos diseños.

Las capacidades de los dispositivos lógicos programables a gran escala, como las matrices de compuertas programables en campo (FPGA) y los dispositivos lógicos programables complejos (CPLD), han existido desde su primera introducción hace décadas como reemplazos de la lógica de unión y como dispositivos de creación de prototipos ASIC, está creciendo rápidamente. . Los aceleradores y microprocesadores integrados son fuertes candidatos para muchas aplicaciones que alguna vez se consideraron dominio exclusivo de DSP y ASSP. Una comprensión básica de las arquitecturas FPGA y CPLD puede mejorar el rendimiento, la eficiencia y el ciclo de diseño de muchos diseños.

La lógica programable tiene una larga historia de desarrollo antes de alcanzar sus formas más avanzadas en FPGA y CPLD. La diferencia arquitectónica entre las dos tecnologías está indicada por el propio nombre. Los FPGA tienen una estructura muy similar a los ASIC Gate Array y, de hecho, se usaron originalmente para la creación de prototipos de ASIC. Un CPLD es una red de elementos lógicos programables conectados para crear un sistema más grande.

Fundamentos de la lógica programable

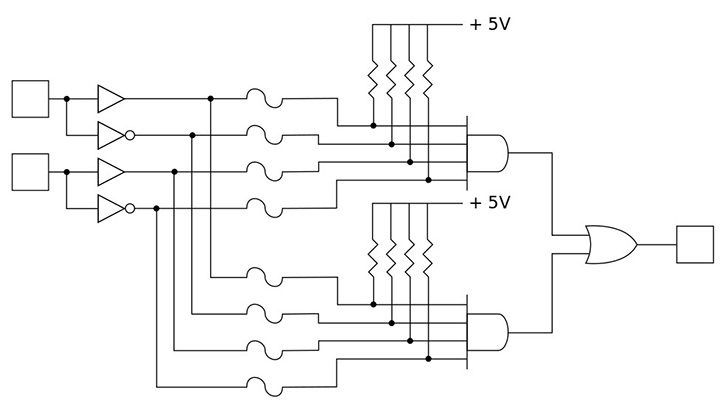

La idea de configuraciones básicas de FPGA y CPLD se puede entender rápidamente al revisar las características de la lógica de matriz programable (PAL). PAL comienza con un amplio plano AND programable para aplicar AND a las entradas. El plano OR es fijo, lo que limita el número de términos que se pueden combinar con OR. Agrega dispositivos lógicos básicos como multiplexores, OR exclusivos y pestillos, y también incluye elementos de reloj como flip-flops.

Esta combinación de elementos de circuito permite a los diseñadores implementar numerosas funciones lógicas, incluida la lógica secuencial sincronizada necesaria para las máquinas de estado. PAL es un dispositivo muy rápido y ha reemplazado gran parte de la lógica estándar en los diseños de generaciones anteriores. La Figura 1 muestra un PAL básico donde un elemento programable (que se muestra como un fusible) conecta las entradas verdadera y complementaria a una puerta AND. Las compuertas AND, también conocidas como términos de productos, se combinan para formar una matriz lógica de suma de productos.

Los CPLD y los FPGA crean un medio altamente escalable y satisfactorio entre los arreglos de puertas PAL y ASIC. CPLD es tan rápido como PAL pero más complejo. Los FPGA abordan la complejidad de los arreglos de puertas y son programables.

arquitectura CPLD

Cada proveedor de CPLD tiene su propia implementación, pero todos los CPLD tienen una característica común: consisten en bloques de funciones (FB), bloques de entrada/salida (E/S) y una matriz de interconexión. Los CPLD se programan utilizando elementos específicos de la tecnología del fabricante. Los dispositivos de memoria pueden ser celdas EPROM, celdas EEPROM o celdas Flash EPROM. La Figura 2 muestra la arquitectura de un CPLD típico.

arquitectura FPGA

Las arquitecturas FPGA son similares a las ASIC, pero completamente diferentes a las CPLD. Una arquitectura FPGA típica consta de un conjunto de bloques lógicos configurables (CLB), pads de E/S e interconexiones programables, como se muestra en la Figura 3. Se agrega un circuito de reloj para conducir la señal de reloj a cada bloque lógico. Las unidades aritméticas lógicas, las memorias y los decodificadores también son elementos típicos.