Continuando con la segunda y última entrega de esta serie, nos centraremos en la segunda suite de desarrollo de software, Analytical Software Design Suite (ASD:Suite). Es un motor de verificación formal que permite la verificación de diseños de sistemas de software.

Continuando con la segunda y última entrega de esta serie, nos centraremos en la segunda suite de desarrollo de software, Analytical Software Design Suite (ASD:Suite). Es un motor de verificación formal que permite la verificación de diseños de sistemas de software.

TEA:Suite®, Verum®

Para sistemas críticos de seguridad complejos con muchos componentes de software, la verificación formal del sistema es aún más importante. Verum® aborda estos requisitos al ofrecer ASD:Suite® (Analytical Software Design Suite). ASD:Suite® (Analytical Software Design Suite) es un motor de verificación formal altamente sofisticado que permite la verificación de diseños de sistemas de software mucho antes en el ciclo de diseño, antes de codificar o a nivel de sistema. Una herramienta de diseño basada en modelos. prueba. Esto no solo permite un desarrollo de software más rápido, sino que también garantiza una alta calidad y confiabilidad del software.

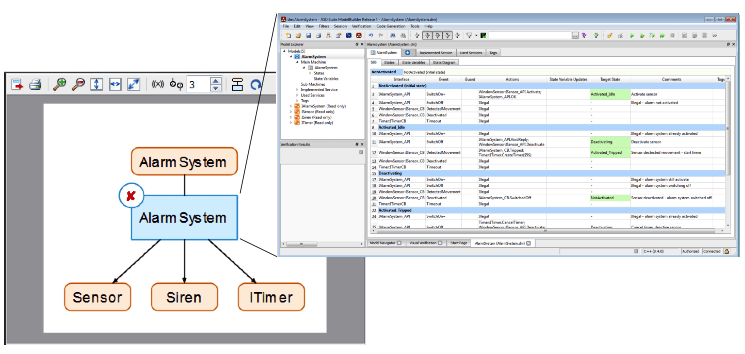

El IDE de ASD:Suite le permite crear y administrar componentes de software y definir interfaces entre varios componentes. Un editor basado en tablas llamado navegador de modelos le permite expandir cada componente y definir su modelo de comportamiento.

Una vez que se crea el modelo, ejecute el motor de validación formal para detectar problemas de concurrencia, interbloqueos, bloqueos dinámicos, condiciones inalcanzables, comportamiento incorrecto, condiciones de carrera, discrepancias de interfaz, errores no controlados y comportamiento incompleto. Puede detectar errores como También puede crear seguimientos (anotaciones) de condiciones que desencadenan errores. Para validar completamente el modelo, puede ser necesario crear un modelo del sistema externo que interactúe con el componente de software.

Una vez que se valida su modelo, puede generar código C, C++, C# e incluso Java. El modo verificado no debe tener un comportamiento indefinido o ambiguo y debe ser totalmente coherente con el flujo de verificación formal, por lo que ASD:Suite garantiza que el código generado sea totalmente equivalente al modelo definido. Podemos garantizarlo. Evite los errores de codificación humanos mediante el uso de la generación automática de códigos. Además, una función llamada generador TinyC puede generar código compacto destinado a sistemas integrados con huellas de memoria limitadas, pero esto limita el diseño a la ejecución de un solo subproceso.

El código generado se puede integrar en proyectos integrados. El código generado puede ejecutarse en varias plataformas e integrarse con RTOS y objetivos bare metal. Además, el diseño es independiente del idioma, por lo que el diseño de un solo modelo se puede trasladar a varias plataformas.

Autor: José Yu

Haga clic para descargar la versión completa en PDF http://community.arm.com/docs/…

parte 1

parte 2

parte 3

parte 4

parte 5

parte 6

Parte 7

parte 8

parte 9

parte 10

parte 11

parte 12