Una máquina de estados finitos (FSM) es un modelo computacional matemático utilizado en el diseño de circuitos lógicos. La parte 10 de esta serie describe VisualSTATE, una de las dos suites de desarrollo de software y aplicaciones de control de interés.

Una máquina de estados finitos (FSM) es un modelo computacional matemático utilizado en el diseño de circuitos lógicos. La parte 10 de esta serie describe VisualSTATE, una de las dos suites de desarrollo de software y aplicaciones de control de interés.

Diseño de control y FSM

Muchas aplicaciones integradas, especialmente las aplicaciones de control, pueden ver el funcionamiento del sistema como una máquina de estados finitos (FSM). Tenemos una amplia gama de suites de desarrollo de software y aplicaciones de control, incluidos los diseños de FSM. Solo dos de estos están cubiertos aquí.

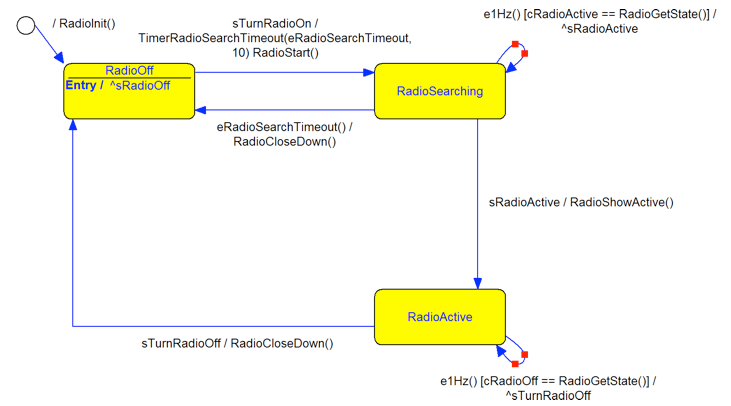

El entorno de diseño de VisualSTATE se basa en UML (Lenguaje de modelado unificado). Las transiciones de estado son provocadas por “eventos”. Por ejemplo, en la siguiente figura, un FSM simple para una unidad controlada por radio se define con tres estados. En cada descripción de transición de estado, el texto a la izquierda de ‘/’ describe el evento que desencadenó la transición, y el texto a la derecha de ‘/’ describe la acción realizada en la transición de estado.

VisualSTATE le permite definir eventos internos (llamados señales indicadas por el prefijo ‘^’) que pueden activarse como parte del lado de acción de una transición. Dichos eventos de señalización se procesan antes que los nuevos eventos del entorno. Se puede especificar una condición de protección como parte de la definición del activador y debe ser verdadera para que se produzca la transición. Las condiciones de protección se definen mediante expresiones booleanas con una sintaxis similar a C.

VisualSTATE le permite crear máquinas de estado y definir fácilmente las operaciones de la máquina de estado. Una vez diseñada la máquina de estado, VisualSTATE genera código C/C++ que se puede integrar en un proyecto regular en IAR Embedded Workbench® para ARM (EWARM).

Para ayudar a los desarrolladores, Visual State incluye validadores formales que pueden detectar problemas potenciales como:

- interbloqueo (nivel local o del sistema)

- estado inalcanzable o combinación de estados

- transiciones conflictivas

- Sistema con comportamiento ambiguo

Las secuencias de transición que desencadenan estos errores se pueden anotar con herramientas de depuración. IAR VisualSTATE está estrechamente relacionado con IAR EWARM para que se pueda depurar con el depurador C Spy con el sistema de destino de hardware conectado. El código FSM generado también puede ejecutarse como subprocesos en un entorno RTOS.

Autor: José Yu

Haga clic para descargar la versión completa en PDF http://community.arm.com/docs/…

parte 1

parte 2

parte 3

parte 4

parte 5

parte 6

Parte 7

parte 8

parte 9

parte 10

parte 11

parte 12