Dado que los sistemas integrados se adaptan a aplicaciones más avanzadas, también se requieren sistemas avanzados de memoria externa como DDR3 para proporcionar un rendimiento adecuado. Para validar y depurar adecuadamente su sistema prototipo, puede ser muy útil ver la actividad de la memoria y realizar algún análisis de memoria. Una nueva opción lo hace posible y tiene un precio muy bajo en comparación con el pasado reciente Proporcione herramientas de análisis relevantes para proporcionar.

prólogo

Dado que los sistemas integrados se adaptan a aplicaciones más avanzadas, también se requieren sistemas avanzados de memoria externa como DDR3 para proporcionar un rendimiento adecuado. Para validar y depurar adecuadamente su sistema prototipo, puede ser muy útil ver la actividad de la memoria y realizar algún análisis de memoria. Una nueva opción lo hace posible y tiene un precio muy bajo en comparación con el pasado reciente Proporcione herramientas de análisis relevantes para proporcionar.

Para respaldar el objetivo de reducir el costo de estas mediciones, el decodificador DDR3 en la solución se modificó para operar solo con señales de dirección y comando, reduciendo así la cantidad total de canales necesarios para mediciones significativas. Por ejemplo, un nuevo sistema básico de 34 canales de la serie Agilent 16850 puede realizar mediciones y análisis de estado de comando y dirección DDR3 1333 (síncrono) por aproximadamente $36,000. Anteriormente, una solución de analizador lógico capaz de proporcionar tales mediciones y análisis requería un presupuesto de aproximadamente $100,000.

Requisitos de sondeo para mediciones DDR3

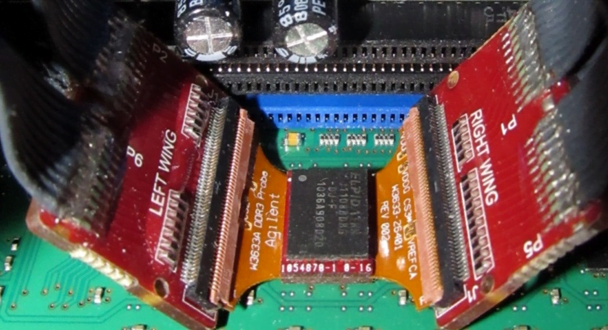

Para realizar mediciones en tiempo real en la interfaz entre un controlador de memoria DDR3 y un dispositivo de memoria, la señal debe probarse de manera que proporcione una imagen precisa de la señal sin introducir una distorsión significativa. Una buena opción de sondeo para diseños con memoria integrada es usar una sonda BGA, como se muestra en la Figura 1. Las señales de dirección, comando y datos se interceptan y envían al analizador lógico mediante un cable plano coaxial. Una red de terminación al final de la sonda proporciona una conexión de alta impedancia de 20 kΩ de resistencia y una carga capacitiva concentrada de 1,3 pF. Dichos esquemas de prueba son viables hasta velocidades DDR3 de 2500 megabits por segundo. Esta configuración proporciona mucho margen para las mediciones DDR3 1333 realizadas en analizadores lógicos de bajo costo.

Otras opciones de sondeo incluyen el uso de intercaladores DIMM o sondas mid-bus. El sondeo de bus medio implica colocar una almohadilla o conector de conexión en algún lugar a lo largo de las huellas de memoria de la placa de PC entre el IC que contiene el controlador de memoria y el IC de memoria. Luego, las sondas se ponen en contacto con estas almohadillas o enchufes y se conectan a los conectores para acceder a las señales DDR3.

Las sondas BGA tienen la ventaja de que no se requieren modificaciones especiales en la placa de circuito impreso, aparte de garantizar que haya suficiente volumen de bloqueo (kov) para que la sonda encaje. Los analizadores lógicos también vienen con archivos de configuración para usar dichas sondas.

Descodificación de bus DDR3

Una herramienta de análisis que ayuda a los diseñadores a comprender mejor cómo se comporta realmente la memoria DDR3 externa es el decodificador de memoria. Este software toma las señales de estado de comando y dirección de obtención sin procesar y las convierte a un formato mucho más comprensible, como se muestra en la Figura 2. Los comandos de memoria como “escribir” y “leer” se muestran con su selección de chip asociada, dirección de banco y dirección de fila. y la información de la dirección de la columna. Aparecerán otros comandos como “Activar” y “Deseleccionar”. Esta captura de seguimiento del modo de estado se almacena en la memoria profunda, ya que refleja una gran cantidad de tiempo de actividad objetivo. El analizador lógico de bajo costo tiene una frecuencia de reloj de entrada máxima de 700 MHz y es capaz de capturar el estado de direcciones y señales de comando a 667 MHz con memoria DDR3 1333.

Análisis de rendimiento

Aunque es conveniente, una captura sin formato de memoria profunda típica y la salida del decodificador de memoria asociada brindan más información que la que un usuario del analizador lógico puede evaluar fácilmente de forma manual. Sin embargo, las herramientas de rendimiento DDR toman toda la información capturada y decodificada y la procesan en varias vistas orientadas al rendimiento para proporcionar un análisis útil. Cuatro ejemplos de vistas de resumen incluyen Resumen, Estadísticas de actualización, Histograma de direcciones y Velocidad de datos efectiva, como se muestra en la Figura 3.

La distribución esperada del ciclo de memoria se puede verificar utilizando la “vista de distribución del ciclo” de la herramienta de análisis de rendimiento para un modo particular de operación de destino. Por ejemplo, es fácil ver si el sistema de destino dedica mucho tiempo a “anular la selección” de la memoria.

Aunque el prototipo funciona funcionalmente, es posible que falte el rendimiento general del sistema. Ver las tasas de datos de lectura y escritura puede revelar problemas en el diseño del controlador de memoria. El factor de eficiencia general también puede indicar un problema. Ahora, una eficiencia del 51 % no es necesariamente mala, pero puede que no sea adecuada para su aplicación. Cuando se usa un espacio de direcciones de memoria, el controlador de memoria generalmente debe pasar poco tiempo accediendo a una pequeña cantidad de ubicaciones de memoria y debe distribuir esos accesos a la memoria en un rango. Una vista de histograma del espacio de memoria al que se accede puede revelar “puntos calientes” que pueden conducir a fallas prematuras de la memoria.

prueba de cumplimiento de memoria

Otro tipo de evaluación de la memoria que es útil durante el encendido del prototipo es la prueba de conformidad con las especificaciones JEDEC. Esta evaluación puede revelar errores en el diseño del controlador de memoria. El incumplimiento de la especificación puede dar lugar a errores en los datos. Se encuentra disponible una herramienta de cumplimiento de post proceso DDR que también funciona a partir de las señales de memoria de dirección y comando almacenadas en la memoria del analizador lógico. El tipo de sonda de memoria se selecciona junto con el tipo de memoria a evaluar, su tasa de datos y la prueba deseada. Con esta información, se puede probar un conjunto de parámetros de evaluación utilizando herramientas de cumplimiento.

La Figura 4 muestra los resultados de tal prueba. Aquí, la falla se encontró en cuatro operaciones de “activación” que se originaron en diferentes bancos de memoria.

Seleccione una fila con los errores resaltados para ver la cantidad de errores encontrados para una operación en particular en comparación con el total de esa operación. También enumera el par de estado exacto asociado con cada recuento de errores en el seguimiento de la memoria profunda. Es importante no solo informar que se han producido errores, sino también identificar la ubicación específica de esos errores para que se pueda rastrear la causa raíz de la falla. Las herramientas de cumplimiento en tiempo real también activan analizadores lógicos sobre violaciones.

Captura de modo de tiempo de dirección, comando, lectura de memoria y escritura de datos

Todas las medidas hasta ahora han sido medidas de estado (sincrónicas), pero las medidas de tiempo (asincrónicas) también son útiles, incluidas las medidas de datos de lectura y escritura para rastrear el flujo de datos de la memoria. Para el sistema de memoria DDR3 1333 evaluado aquí, las mediciones del modo de temporización requieren una frecuencia de muestreo de temporización lo suficientemente rápida como para determinar la actividad del bus. Una buena regla general es una proporción de 3:1 entre la frecuencia de muestreo del analizador lógico y la frecuencia de datos del sistema de destino.

Para velocidades de datos 1333, esto se traduce en velocidades de sincronización de 4 GHz y superiores. Los analizadores lógicos portátiles de bajo costo están disponibles con velocidades de temporización de 5 GHz de medio canal que cumplen con este requisito. El analizador incluye configuración de modo de temporización de medio canal para dirección, comando y captura de datos. En la Figura 5 se muestra un ejemplo de captura.

Se requiere un modelo de 102 canales para proporcionar 48 canales en modo de medio canal para que se puedan capturar datos de dirección, comando y x8 o x16 para esta medición. Los datos de lectura y escritura no se separan en la captura de tiempo, pero los valores de lectura y escritura del bus de datos establecidos se muestran en la línea DATA con la configuración de división de tiempo ampliada. Si necesita una captura de estado de datos de lectura y escritura separada, existen soluciones de analizador lógico modular que pueden lograrlo.

Requisitos del analizador lógico específicos para ciertas aplicaciones de memoria

La figura 6 resume la funcionalidad de los modos de temporización y estado. Esto incluye el uso de decodificadores DDR y conjuntos de herramientas de análisis y cumplimiento de protocolos.

resumen

Se convirtió en un analizador lógico portátil de propósito general de 34 canales de bajo costo en modo de estado (síncrono) para capturar direcciones DDR3 1333 y señales de comando para decodificación de memoria, análisis de rendimiento y pruebas de cumplimiento para ayudar en la verificación y depuración. Diseño digital. Además, al usar el modo de medio canal de 5 GHz en el analizador de 102 canales, las formas de onda de la dirección DDR3 1333, las señales de comando y datos de la DRAM se pueden mostrar para ayudar en la evaluación general del sistema. La decodificación del tráfico DDR3 no se admite en el modo de temporización, pero la visualización de formas de onda de temporización puede proporcionar información valiosa de depuración. El analizador modular se puede utilizar para la captura de estado mediante decodificación de memoria para separar datos de lectura y escritura en memorias de alta velocidad con altas tasas de datos, como sistemas DDR4, LPDDR2/3, LPDDR4 o DDR3 1333.