Esta nota de aplicación presenta las características principales del procesador ARM Cortex-M3 y cubre varios aspectos del desarrollo de software. También cubre la migración de proyectos ARM existentes a la plataforma Cortex-M3.

Corteza-M3

El ARM Cortex-M3 es un procesador RISC de 32 bits de alto rendimiento, bajo costo y bajo consumo. El procesador Cortex-M3 solo ejecuta instrucciones Thumb-2. El conjunto de instrucciones ARM no es compatible. El procesador Cortex-M3 se basa en la arquitectura ARM v7-M y cuenta con un eficiente núcleo de canalización de 3 etapas de Harvard. También cuenta con partición de hardware y entrada y salida de rutina de servicio de interrupción (ISR) de baja latencia.

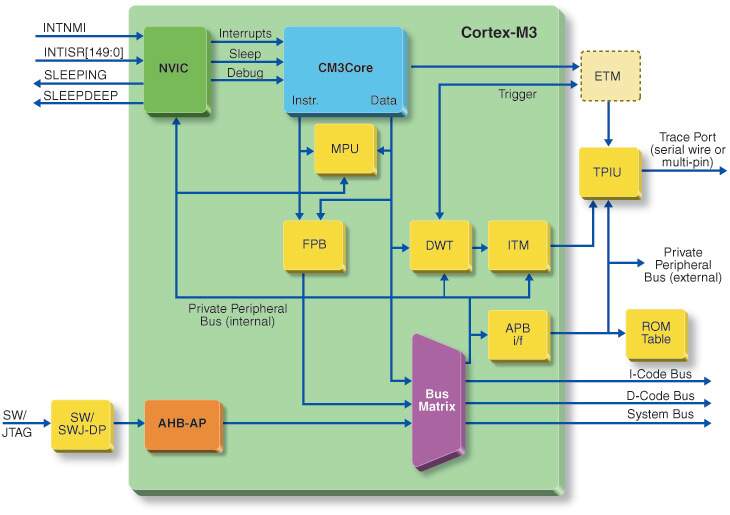

Además de los núcleos de CPU, los procesadores Cortex-M3 contienen muchos otros componentes. Estos incluyen un controlador de interrupción vectorial anidado (NVIC), una unidad de protección de memoria (MPU) opcional, temporizadores, un puerto de acceso de depuración (DAP) y una macrocelda de seguimiento integrada (ETM) opcional. Cortex-M3 también tiene un mapa de memoria fijo.

Controlador de interrupción vectorial anidado (NVIC)

Según la implementación utilizada por el fabricante de silicio, la NVIC puede admitir hasta 240 interrupciones externas con hasta 256 niveles de prioridad diferentes que se pueden volver a priorizar dinámicamente. Admite fuentes de interrupción de nivel y de pulso. El hardware guarda automáticamente el estado del procesador a la entrada de una interrupción y lo restaura al final de la interrupción. NVIC también admite el encadenamiento final de interrupciones.

El uso de NVIC en Cortex-M3 significa que la tabla de vectores de Cortex-M3 es muy diferente de los núcleos ARM anteriores. La tabla de vectores Cortex-M3 contiene las direcciones de los controladores de excepciones e ISR, no instrucciones como la mayoría de los otros núcleos ARM. El puntero de pila inicial y las direcciones del controlador de reinicio deben ubicarse en 0x0 y 0x4 respectivamente. Estos valores se cargan en los registros de CPU apropiados en el reinicio.

Unidad de protección de memoria (MPU)

MPU es un componente opcional de Cortex-M3. Cuando se incluye, brinda soporte para proteger regiones de memoria mediante la aplicación de privilegios y reglas de acceso. Admite hasta 8 regiones diferentes, cada una de las cuales se puede subdividir en 8 subregiones de igual tamaño.

Puerto de acceso de depuración (DAP)

Los DAP usan la interfaz AHB-AP para comunicarse con procesadores y otros periféricos. Hay dos implementaciones de puerto de depuración admitidas: puerto de depuración JTAG de cable serie (SWJ-DP) y puerto de depuración de cable serie (SW-DP). Una implementación de Cortex-M3 puede incluir uno de estos, según la implementación utilizada por el fabricante de silicio.

mapa de memoria

A diferencia de la mayoría de los núcleos ARM anteriores, los dispositivos basados en Cortex-M3 tienen un diseño de mapa de memoria general fijo. Esto facilita la transferencia de software entre diferentes sistemas basados en Cortex-M3. El espacio de direcciones se divide en varias secciones diferentes. Esto se muestra en la Figura 2 a continuación.