Esta nota de aplicación presenta el controlador DMA de la CPU ZNEO y otras características interesantes, como el control compartido de ancho de banda DMA y CPU, y 4 canales DMA independientes. Este documento también cubre los modos DMA, la implementación del software y la prueba/demostración de la aplicación.

característica

Las funciones destacadas de acceso directo a la memoria de la CPU ZNEO son:

- 4 canales DMA independientes

- Admite transferencias de datos de memoria a memoria, de memoria a periférico, de periférico a memoria y de periférico a periférico.

- Funciona en modo de lista directa o enlazada

- Longitud de transferencia de datos de bytes, palabras o cuádruples

- Control de uso compartido de ancho de banda de DMA y CPU

- Transferencias de hasta 64 K (64 kByte, 64 kWord o 64 kQual)

- Solicitud de DMA externa y señales de reconocimiento de DMA

discusión

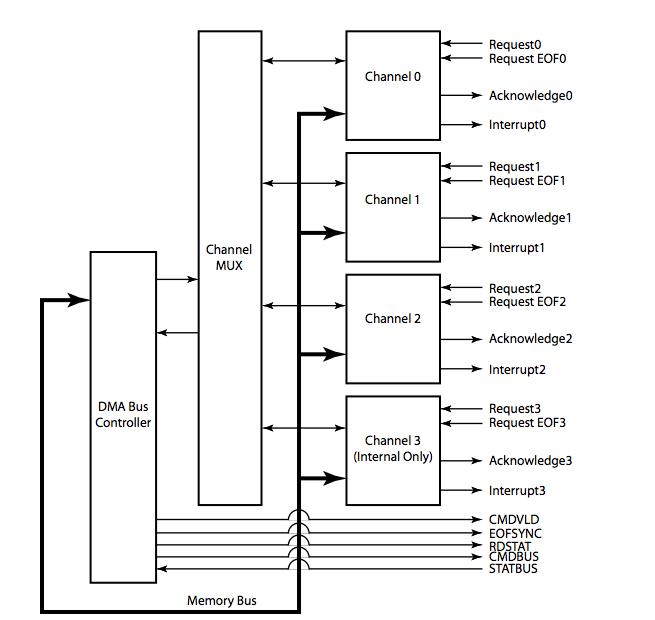

ZNEO DMA se utiliza para evitar que el procesador realice tareas repetitivas. Transferir datos de una dirección de memoria a otra dirección de memoria o de un periférico a otro. Estas tareas requieren ciclos de lectura y/o escritura generados por el controlador DMA. Se requiere un mínimo de dos ciclos de reloj del sistema para realizar cada transferencia DMA. La Figura 1 muestra un diagrama de bloques del controlador DMA para MCU Z16F basado en la arquitectura ZNEO.

modo DMA

El modo directo usa solo registros dentro del DMA para operaciones. El software escribe directamente en estos registros para configurar y habilitar DMA. Se ingresa al modo directo configurando directamente los bits apropiados en el registro DMAxCTL0. El siguiente diagrama muestra los registros DMA y cómo apuntan a los búfer asignados a la memoria.

Modo de lista de enlaces

En el modo de lista enlazada, el software debe asignar búferes y configurar una lista de descriptores para cada búfer. Una vez hecho esto, el software escribe la dirección del primer descriptor en DMAxLAR. El DMA luego carga el primer descriptor en los registros de dirección y control de DMA, excluyendo los datos LAR. Ejecuta la transferencia según lo especificado por los datos del descriptor DMA. Una vez que se completa la transferencia, el DMA lee el siguiente descriptor en la lista y continúa ejecutando la transferencia.

Implementación de software

Este diseño de referencia utiliza el kit de desarrollo ZNEO Z16F2800100ZCOG. Esto utiliza el controlador DMA de la CPU ZNEO, específicamente el canal 0 de DMA, para fines de demostración. La aplicación también utiliza UART0 para proporcionar una consola basada en menús que permite al usuario probar los distintos modos de funcionamiento del controlador DMA. Además, admite demostraciones de DMA utilizando periféricos como ADC, Timer2 y UART1. Consulte el Apéndice A para la inicialización de periféricos.

Selección de ancho de banda de la CPU

Antes de inicializar DMA, asegúrese de que el bus de la CPU esté configurado para asignar el ancho de banda requerido para el uso de DMA. Si no se establece, se utilizará el valor de reinicio. En otras palabras, al DMA se le permite 1 transferencia por cada 3 operaciones de CPU. Esta nota de aplicación proporciona ejemplos de diferentes valores de CPUCTL usando diferentes selecciones de ancho de banda. La siguiente tabla muestra el ancho de banda de la CPU utilizado por tipo de transferencia. Tanto el modo directo como el modo de lista enlazada usan el mismo ancho de banda de CPU.

resultado

El modo directo se probó con los bits IEOB y EOF en DMA0CTL establecidos en 1 y sin valor de marca de agua establecido. Es decir, las interrupciones solo se generan al final del búfer actual. El modo de lista enlazada se probó usando la misma configuración que el modo directo con el bit HALT en DMA0CTL establecido en 1.