El kit de diseño de sistema Cortex-M (CMSDK) es un producto muy útil para los diseñadores de chips y diseñadores de FPGA que utilizan procesadores ARM Cortex-M. Incluye una amplia gama de componentes de infraestructura de bus AMBA, sistemas de ejemplo, periféricos de ejemplo, componentes de verificación y scripts de síntesis. Aquí hay 10 datos sobre CMSDK que pueden resultarle útiles.

El kit de diseño de sistema Cortex-M (CMSDK) es un producto muy útil para los diseñadores de chips y diseñadores de FPGA que utilizan procesadores ARM Cortex-M. Incluye una amplia gama de componentes de infraestructura de bus AMBA, sistemas de ejemplo, periféricos de ejemplo, componentes de verificación y scripts de síntesis. Aquí hay 10 datos sobre CMSDK que pueden resultarle útiles.

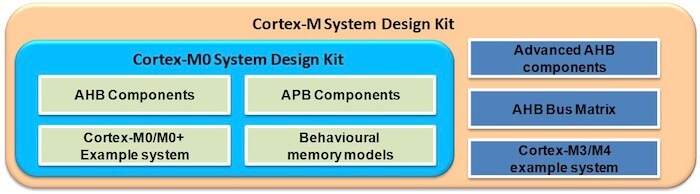

1) elección – CMSDK tiene dos ediciones. La versión completa de CMSDK proporciona una amplia gama de componentes de infraestructura de bus para admitir diseños AHB mixtos de 64 bits y 32 bits, proporcionando puentes de bus para conectar segmentos de bus con diferentes velocidades de reloj. Si tiene un diseño de sistema simple con procesadores Cortex-M0 o Cortex-M0+, use el kit de diseño de sistema Cortex-M0 más pequeño que proporciona componentes esenciales para construir sistemas más simples.

2) Flexibilidad – Muchos de los componentes de CMSDK ya se pueden configurar mediante parámetros de Verilog. Además, los términos de la licencia de CMSDK le permiten modificar los sistemas y componentes de ejemplo de CMSDK para adaptarlos a su aplicación.

3) Admite múltiples maestros de bus – Ambas versiones completas de CMSDK admiten diseños con múltiples maestros de bus. Los multiplexores maestros 3:1 fáciles de usar están disponibles en ambas versiones. Una matriz de bus AHB configurable está disponible en la versión completa de CMSDK. Esto permite hasta 16 puertos maestros y 16 puertos esclavos, lo que permite el acceso simultáneo de múltiples maestros a múltiples esclavos.

cuatro) Componente de validación – CMSDK incluye varios componentes de verificación, como el comprobador de protocolo de bus AHB Lite. Estos se utilizan normalmente en simulaciones para detectar violaciones del protocolo de bus. También se puede utilizar para ayudar con la verificación formal. Otro componente de validación útil es File Reader Bus Master. Esto es para generar estímulos de transferencia de bus en simulación, incluidos escenarios que el procesador no puede generar.

Cinco) Características avanzadas del puente AHB a APB – Un componente puente síncrono de AHB a APB permite que el segmento de bus APB funcione a la misma frecuencia que el AHB o con una relación de reloj dividida. También tiene una salida de estado del bus que se puede usar para desactivar la señal del reloj del bus periférico cuando no se realizan transferencias. Esto puede reducir significativamente el consumo de energía.

6) Soporte de puente asíncrono – La versión completa de CMSDK tiene un puente AHB Lite a APB asíncrono, lo que permite que el segmento de bus APB se ejecute a una frecuencia de reloj completamente diferente. Al igual que la versión síncrona, también tiene una señal de salida de control de activación de reloj de bus. En la revisión 1 del kit de diseño, se agregó al kit un puente asíncrono AHB a AHB. Este componente de puente también proporciona un puerto APB opcional para que un componente de puente pueda unir dos segmentos de bus.

7) Diseño de sistema robusto – El kit de diseño tiene un monitor de tiempo de espera AHB y un monitor de tiempo de espera APB. Un monitor puede conectarse directamente a un esclavo de bus y devolver una respuesta de error si el esclavo de bus está colgado y no puede responder dentro de una cierta cantidad de ciclos de reloj. Esto evita que una falla del bus esclavo bloquee todo el sistema del procesador.

8) soporte de herramientas – CMSDK está diseñado para admitir una amplia variedad de herramientas, como Mentor Modelsim/Questasim, Cadence Incisive/NC Sim, Synopsys VCS, la cadena de herramientas de compilación ARM, Keil Microcontroller Development Kit (MDK), gcc.

9) Fácil integración SRAM – CMSDK tiene un componente de puente AHB Lite a SRAM que permite que la SRAM síncrona en el chip se conecte a AHB sin estados de espera. Además, hay módulos de interfaz de memoria SRAM externos que admiten SRAM de 16 y 8 bits o periféricos externos.

Diez) Fácil migración de diseño – Al migrar periféricos de arquitecturas de 8 o 16 bits a ARM, el ejemplo de esclavo de bus en CMSDK es un buen ejemplo de cómo conectar registros periféricos a AHB Lite o APB. El diseño esclavo de ejemplo se divide en un módulo de interfaz de bus y un bloque de registro. Los módulos de interfaz de bus se pueden reutilizar directamente para conectar la mayoría de los periféricos heredados a AHB Lite o APB.