Los contadores almacenan combinaciones digitales de datos. Los contadores se utilizan en todas partes de la vida diaria. Un ejemplo es un reloj despertador digital que te despierta temprano en la mañana.

Hay dos tipos de contadores.

- 1) Sincronización y

- 2) Asincrónico.

descripción general

Tabla de contenido

contador asíncrono

Un contador asíncrono es un contador cuya salida no incluye una señal de reloj. Los flip-flops de un contador asíncrono reciben diferentes señales de reloj, lo que puede provocar un retraso en la producción de la salida.

El número de puertas lógicas necesarias para diseñar un contador asíncrono es muy pequeño. Por tanto, el diseño es sencillo. Otro nombre para los contadores asíncronos es “contadores de ondulación”.

La cantidad de flip-flops utilizados en un contador de ondulación depende de la cantidad de estados del contador (por ejemplo, Mod 4, Mod 2, etc.). El número de estados de salida de un contador se denomina “módulo” o “MOD” del contador. El número máximo de estados que puede tener un contador es 2n. Aquí, n representa el número de flip-flops utilizados en el contador.

Por ejemplo, si hay dos flip-flops, el número máximo de salidas de contador es 4 o 22. Por eso se llama “contador MOD-4” o “contador de módulo 4”.

Diferentes tipos de contadores asíncronos

En la electrónica digital se encuentran disponibles diferentes tipos de contadores asíncronos.ellos son

- Contador Ascendente síncrono de 4 bits

- Contador descendente síncrono de 4 bits

- Contador ARRIBA/ABAJO síncrono de 4 bits

Contador Ascendente asíncrono de 4 bits

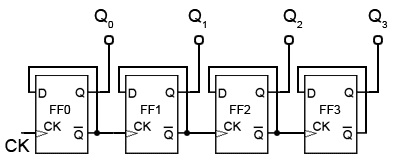

La figura anterior muestra un contador UP asíncrono de 4 bits con un flip-flop D. Puede contar números del 0 al 15. Las entradas de reloj de todos los flip-flops están en cascada y la entrada D (entrada de DATOS) de cada flip-flop está conectada a la salida de estado del flip-flop.

En otras palabras, el flip-flop conmuta en cada flanco activo o positivo de la señal del reloj. La entrada del reloj está conectada al primer flip-flop. Los otros flip-flops en el contador reciben su entrada de señal de reloj desde la salida Q’ del flip-flop anterior. Cuando ocurre un flanco positivo de la señal del reloj, la salida del primer flip-flop cambia.

En el contador ascendente asíncrono de 4 bits, los flip-flops están conectados en modo de conmutación, por lo que si la entrada del reloj está conectada al primer flip-flop FF0, la salida será 20 después de un pulso de reloj.

El flanco ascendente de la salida Q de cada flip-flop activa la entrada de reloj del siguiente flip-flop. Active la siguiente frecuencia de reloj a la mitad de la entrada aplicada. La salida Q de cada flip-flop (Q0, Q1, Q2, Q3) representa el conteo de un contador ARRIBA de 4 bits, como 20 (1) a 23 (8).

El funcionamiento del contador ascendente asíncrono se explica a continuación.

Suponga que las cuatro salidas Q de los flip-flops son inicialmente 0000. Cuando se aplica un flanco ascendente de un pulso de reloj a FF0, la salida Q0 cambia a lógica 1 y el siguiente pulso de reloj cambia la salida Q0 a lógica 1. Esto significa que el estado de salida del pulso de reloj cambia (cambia de 0 a 1) durante un ciclo.

La entrada de reloj del segundo flip-flop es 1 porque Q’ de FF0 está conectado a la entrada de reloj de FF1. Esto hace que la salida de FF1 sea Alta (es decir, Q1 = 1), indicando el valor 20. De esta manera, el siguiente pulso de reloj hace que Q0 vuelva a subir.

Por lo tanto, Q0 y Q1 son ambos Altos y la salida de 4 bits es 11002. La aplicación del cuarto pulso de reloj ahora lleva Q0 y Q1 al estado Bajo y alterna FF2. Por tanto, la salida Q2 será 0010ñ2. Dado que este circuito es un contador ascendente de 4 bits, la salida será una secuencia de 0, 1, 2, 3….15 valores binarios, o 00002 a 11112 (0 a 1510).

Por ejemplo, si el recuento actual = 3, el contador ascendente calcula el siguiente recuento como 4.

Contador ABAJO asíncrono de 4 bits

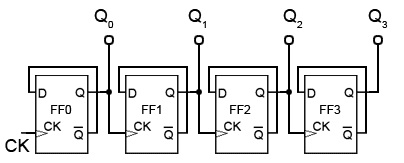

En la figura anterior se muestra un contador ABAJO asíncrono de 4 bits. Esta es una modificación simple del contador ARRIBA. El contador DOWN de 4 bits cuenta atrás de 15 a 0. Las entradas de reloj de todos los flip-flops están en cascada y la entrada D (entrada de DATOS) de cada flip-flop está conectada al 1 lógico.

Esto significa que cada flanco activo (flanco positivo) de la señal del reloj conmuta un flip-flop. La entrada del reloj está conectada al primer flip-flop. Los otros flip-flops en el contador reciben su entrada de señal de reloj desde la salida Q del flip-flop anterior en lugar de la salida Q’.

Aquí, Q0, Q1, Q2, Q3 representan el recuento del contador regresivo de 4 bits. Cuando ocurre un flanco positivo de la señal del reloj, la salida del primer flip-flop cambia. Por ejemplo, si el recuento actual = 3, el contador ascendente calcula el siguiente recuento como 2. El reloj de entrada cambia la salida (cuenta) del siguiente flip-flop.

El funcionamiento de un contador descendente es exactamente el opuesto al de un contador ascendente. Aquí, cada pulso de reloj en la entrada disminuye el conteo de un flip-flop individual. Por lo tanto, el contador regresivo cuenta desde 15, 14, 13…0, es decir (0 a 1510) o desde 11112 a 00002.

Tanto los contadores ascendentes como los descendentes están diseñados con asincronización basada en una señal de reloj, pero no se utilizan ampliamente porque no son confiables a altas velocidades de reloj.

¿Qué es la ondulación del reloj?

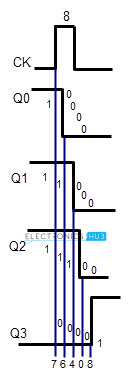

La suma de los retrasos de los pulsos de reloj individuales que impulsan un circuito se denomina “ondulación del reloj”. El siguiente diagrama explica cómo las puertas lógicas crean retrasos de propagación en cada flip-flop.

El retardo de propagación de la puerta lógica está representado por la línea azul. Cada uno de ellos aumenta el retraso del siguiente flip-flop, y la suma de todos estos flip-flops individuales se conoce como retraso de propagación del circuito.

El retardo de propagación de la puerta lógica está representado por la línea azul. Cada uno de ellos aumenta el retraso del siguiente flip-flop, y la suma de todos estos flip-flops individuales se conoce como retraso de propagación del circuito.

La salida de cada flip-flop cambia en diferentes intervalos de tiempo para diferentes entradas de la señal de reloj, lo que da como resultado un nuevo valor en la salida cada vez. Por ejemplo, el pulso de reloj 8 debería cambiar la salida de 11102 (710) a 00012 (810) con un retraso de 400 a 700 ns (nanosegundos).

La secuencia cambiará si no es de 8 relojes.

Aunque este problema impide que este circuito se utilice como un contador confiable, es un divisor de frecuencia simple y efectivo donde un oscilador de alta frecuencia proporciona la entrada y cada flip-flop de la cadena divide la frecuencia por 2. Todavía tiene valor. Se trata de la ondulación del reloj.

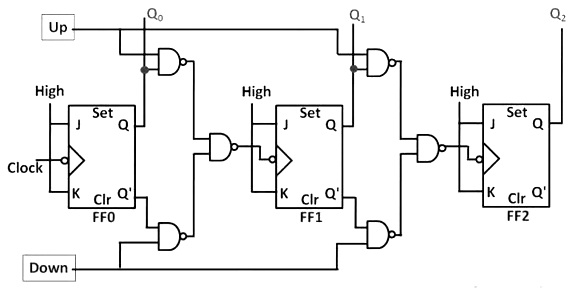

Contador ascendente/descendente asíncrono de 3 bits

Al combinar las ideas de contadores ARRIBA y ABAJO, puede diseñar un contador ascendente/descendente asíncrono. A continuación se muestra un contador ascendente/descendente asíncrono de 3 bits.

Puede contar de arriba a abajo o de abajo a arriba según la entrada de la señal del reloj.

contando

Cuando las entradas ARRIBA y ABAJO son 1 y 0, respectivamente, la puerta NAND entre el primer y tercer flip-flops pasa la salida no inversora de FF 0 a la entrada de reloj de FF 1. De manera similar, la salida Q de FF 1 hace que el contador ascendente/descendente cuente hacia arriba.

cuenta regresiva

Cuando las entradas ABAJO y ARRIBA son 1 y 0, respectivamente, la puerta NAND entre el primer y tercer flip-flops pasa la salida invertida de FF 0 a la entrada de reloj de FF 1. De manera similar, pase también la salida Q de FF 1. Esto hace que el contador ascendente/descendente realice una cuenta regresiva.

Los contadores ascendentes/descendentes son más lentos que los contadores ascendentes y descendentes debido al retraso de propagación adicional en la red de puerta NAND.

ventaja

- Los contadores asíncronos se pueden diseñar fácilmente con flip-flops T o D.

- También se denominan contadores de ondulación y se utilizan en circuitos de baja velocidad.

- Se utilizan como contadores de división por n que dividen la entrada entre n, donde n es un número entero.

- Los contadores asíncronos también se utilizan como contadores truncados. Estos se pueden utilizar para diseñar cualquier contador de números Mod, es decir, mod par (por ejemplo, mod 4) o mod impar (por ejemplo, mod3).

Contras

- Es posible que se requieran flip-flops adicionales para la “resincronización”.

- Se requiere lógica de retroalimentación adicional para contar secuencias de contadores truncados (mod no igual a 2n).

- Cuando se cuenta una gran cantidad de bits, el retraso de propagación de un contador asíncrono es muy grande.

- A altas frecuencias de reloj, los retrasos en la propagación pueden provocar errores de conteo.

Aplicaciones de contadores asíncronos

- Los contadores asíncronos se utilizan como divisores de frecuencia, como los contadores de división por N.

- Se utilizan para aplicaciones de baja potencia y bajas emisiones de ruido.

- Se utilizan para diseñar contadores de décadas asincrónicos.

- También se utiliza para contadores de anillo y contadores Johnson.

- Los contadores asíncronos se utilizan en los contadores de ondulación Mod N. Ejemplos: Mod 3, Mod 4, Mod 8, Mod 14, Mod 10, etc.

Artículo relacionado:

- Multiplexor (MUX) y multiplexación

- Diseño flip-flop T | Circuito usando SR, JK, D…

- SR Flip-Flop – Diseño con puertas y aplicaciones

- Tipos de diseño de circuitos ADC | Flash, sucesivos…

- Símbolos lógicos para puertas lógicas básicas (O, Y, NO,…)

- Distribución de pines ATmega328P | Paquete IC, distribución de pines y descripción de pines