El entretenimiento y el infoentretenimiento modernos en los vehículos modernos exigen capacidades que solo la integración de nuevas tarjetas gráficas de alta velocidad y el almacenamiento de memoria ultrarrápido pueden proporcionar. Todas nuestras interacciones sociales digitales se registran y se implementan como un gran bastidor de computadoras que deben recuperar rápidamente los datos de las unidades de memoria en funcionamiento y alternarlos entre subsistemas para su procesamiento.

Una gran cantidad de imágenes siempre se capturan y almacenan en alta resolución y se pasan a un servidor de IA (inteligencia artificial) en diversas situaciones. Los algoritmos sofisticados procesan los datos rápidamente y producen excelentes resultados.

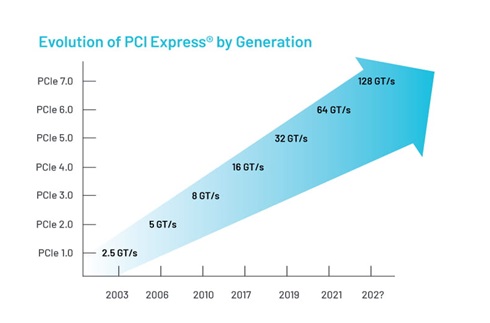

Un servidor de IA típico no es diferente de cualquier otro sistema informático avanzado. La placa base y varios otros dispositivos avanzados, como tarjetas gráficas, discos duros y numerosos conmutadores, están interconectados. La conexión estándar para todos estos dispositivos se basa en el estándar PCI Express (PCIe). Desde que se lanzó la primera generación en 2003, el estándar PCI-SIG® ha continuado persiguiendo una agresiva meta anual de duplicar la tasa de datos con cada generación del estándar PCIe® (Figura 1).

Sin embargo, para adaptarse a tasas de datos más altas, el diseño de sistemas electrónicos se convierte en una tarea de mejora incremental que requiere mucha habilidad y paciencia. El complejo sistema de interconexión de placas base y tarjetas complementarias, incluso después de completar el diseño completo, debe dividirse cuidadosamente en subcircuitos más pequeños, cada uno de los cuales es el objetivo de una fase posterior de mayor refinamiento.

Figura 1: La velocidad de transferencia de datos aumenta con cada generación de PCI Express

PCIe Gen4 ahora está siendo reemplazado por su predecesor en diversas condiciones del mercado a medida que aumentan los requisitos de ancho de banda adicional. Para abordar esto, los ingenieros actualizan constantemente las mejores prácticas de diseño, intercambian sugerencias y pautas para enrutar los carriles de PCB para minimizar las situaciones de diafonía o resolver problemas. EMI Problemas causados por vias colocadas incorrectamente.

Estos ingenieros a menudo son “pioneros” y luchan constantemente para identificar dónde y qué posibles deterioros en la señal pueden ocurrir y cuánto compromiso es aceptable. Un simple cambio de conector a una opción más económica, un cambio menor en el pinout debido a requisitos mecánicos de última hora o limitaciones de la cadena de suministro, una actualización de firmware o hardware, o un cambio en el proceso de producción pueden ser su peor pesadilla, ya que el costo de abordar estos problemas es el tiempo adicional que se dedica a la placa. rediseñar.

La aplicación de una actualización del BIOS a la placa base podría interrumpir la comunicación a toda velocidad con el SSD NVMx, lo que podría cambiar el escenario de la capa física eléctrica. Durante las actualizaciones de firmware, la configuración de los interruptores y temporizadores que se conectan a la placa base y se comunican con la CPU puede cambiar. Ejecutar la “Prueba de margen de carril” después de cambiar estas condiciones puede producir resultados de prueba diferentes. Las mejoras del límite de fluctuación pueden ocurrir en cualquier momento, y el modelado preciso dentro de herramientas de simulación complejas es clave para realizar una verificación “virtual” antes de probar el impacto real en la capa PHY (física) de silicio. Sin embargo, la simulación no representa necesariamente una implementación del mundo real, por lo que aún se deben realizar pruebas de capa física.

Las configuraciones Gen3 y Gen4 de baja potencia se reconfiguran con frecuencia para aplicar posibles configuraciones de ahorro de energía. Un pequeño ajuste en el circuito de alimentación debería hacer que la fase de encendido sea lo suficientemente rápida como para cumplir con los requisitos de duración del tren de enlace, ya que unos pocos incrementos de milisegundos pueden ser problemáticos y generar nuevos escenarios para validar.

Sin embargo, la revalidación del diseño puede no ser rentable en estos escenarios. De hecho, los cambios de diseño menores en productos no críticos y de bajo costo que se venden en aplicaciones de consumo/IoT que todavía usan conectividad PCIe Gen3 no pueden justificar la inversión de tiempo en los laboratorios de prueba de validación.

Las empresas de Silicon Design tienen árboles de decisión complejos que seguir para aplicar criterios de sabiduría para tomar decisiones al realizar nuevos ciclos de prueba de verificación y validación sobre cambios de diseño. Estos árboles se derivan de análisis de valoración de riesgos y costos.

Las herramientas de prueba utilizadas en este contexto suelen ser probadores de tasa de error de bits (BERT) y osciloscopios. Estos dispositivos continúan evolucionando para cumplir con los requisitos de rendimiento de los estándares PCIe de nueva generación y pueden ser muy complejos de usar según la experiencia del usuario.

Los costos de validación y verificación se relacionan no solo con el costo de propiedad de la instrumentación de hardware, sino también con el costo equivalente a tiempo completo de los recursos especializados asignados a la actividad. Los asistentes de software pueden guiarlo a través de un tutorial de la configuración de prueba para cada prueba y garantizar las conexiones eléctricas adecuadas al dispositivo bajo prueba, pero todo el procedimiento que usa un BERT y un osciloscopio con sondas requiere un ojo experto para supervisar todo el proceso.

Como ejemplo, considere la llamada “inicialización de enlace”. Este es un proceso de control de capa física esencial para inicializar la capa física del dispositivo y aplicar algunas configuraciones al enlace. En el funcionamiento normal, este paso se realiza automáticamente, pero si está interesado en la verificación detallada del diseño, necesita un software que codifique datos específicos para que el usuario pueda diagnosticar y monitorear posibles problemas con las señales durante las transiciones de estado. Los BERT se utilizan normalmente para el entrenamiento y la ecualización de enlaces controlados con precisión, cubriendo las tres áreas de prueba principales de esta competencia: cumplimiento, prueba de margen y resolución de problemas. También se requiere un osciloscopio en tiempo real y un software de aplicación sofisticado para automatizar los procedimientos de prueba complejos en el lado del receptor mientras se comunica con el BERT para intercambiar datos sobre los parámetros de configuración.

La prueba de margen también requiere repetir una lista fija de pasos en secuencia para cada carril de la ranura PCIE, incluido el ajuste de la configuración de tiempo de voltaje de disparo. Procedimientos tan largos y complicados que utilizan varios instrumentos sofisticados pueden introducir errores humanos y comprometer la eficiencia de todo el proceso de verificación.

En lugar de buscar alternativas al sistema BERT/Scope, o alternativas a las herramientas Lane Margin (LM) en chip ya disponibles y ampliamente utilizadas, Tektronix ha adoptado un enfoque diferente.

Figura 2: Probador de margen TMT4

El TMT4 Margin Tester, que se muestra en la Figura 2, se basa en Intel Stratix 10 FPGA y proporciona capacidades industriales para evaluar el estado del enlace para dispositivos PCIe Gen 3 y Gen 4.

de TMT4 Margin Tester se conecta a los enlaces de factor de forma PCIe más comunes, como CEM, M.2, U.2 y U.3, lo que le permite conectarse con la mayoría de los dispositivos PCIe disponibles en la actualidad.

Además de mostrar el diagrama del ojo (Figura 3), probador de margen Proporciona información sobre la ecualización utilizada por el receptor para maximizar la altura y el ancho de los ojos generados.

Hay dos datos importantes proporcionados por el sistema para la prueba del transmisor. Es una combinación de diagramas de ojo para cada carril y los preajustes medidos por el receptor del probador de margen (Figura 4). Los valores de entrenamiento del destinatario asociados con el probador de margen se utilizan para abrir el ojo visible.

En el lado de recepción, se puede realizar una evaluación funcional de la ruta de recepción del DUT. De hecho, puede determinar hasta qué punto se puede reducir la amplitud de la señal transmitida desde el probador de margen dentro del rango operativo esperado antes de devolver un error.

Figura 3. TMT4 Margin Tester muestra al usuario un diagrama de ojo en tiempo real

Figura 4. Los parámetros de entrenamiento del enlace del receptor del probador de márgenes brindan información adicional sobre posibles problemas de estado del enlace

El nuevo TMT4 Margin Tester proporciona herramientas adicionales dedicadas a transmitir/recibir herramientas de margen de carril, lo que permite a los usuarios comprender los problemas de estado de los enlaces para dispositivos PCIe Gen 3 y Gen 4 en solo minutos.