Altera Corporation anunció hoy que su sistema de aviónica de seguridad crítica, incluida la versión certificada DO-254/ED-80 del procesador integrado Nios® II de Altera, ha sido certificado por la Agencia Europea de Seguridad Aérea (EASA).

Altera Corporation anunció hoy que su sistema de aviónica de seguridad crítica, incluida la versión certificada DO-254/ED-80 del procesador integrado Nios® II de Altera, ha sido certificado por la Agencia Europea de Seguridad Aérea (EASA). En lugar de desarrollar una solución ASIC personalizada, Thales Avionics implementó una versión crítica para la seguridad del procesador integrado Nios II en Altera® HardCopy® ASIC para usar en su familia de dispositivos electrónicos de reserva integrados. Al aprovechar los procesadores certificados DO-254/ED-80 de Altera, Thales pudo reducir significativamente el tiempo total de desarrollo del sistema al desarrollar una familia de dispositivos de reserva electrónicos integrados.

“Cuando comenzamos a definir nuestra familia de dispositivos de reserva electrónicos integrados, decidimos que desarrollar un ASIC personalizado para cumplir con los objetivos de RTCA DO-254/Eurocae ED-80 era demasiado costoso y requería mucho tiempo”, dijo Jerome Papineau, Gerente de Producto de Thales Avionics. “Al integrar el procesador integrado Nios II, crítico para la seguridad, con HardCopy ASIC, ahorramos casi dos años de tiempo de desarrollo y, al mismo tiempo, ahorramos costos significativos. El procesador ofrece una solución convincente para cumplir con los requisitos de rendimiento y del sistema mientras gestiona la obsolescencia del sistema. El cumplimiento de RTCA DO-254/Eurocae ED-80 Nivel B nos permite integrar con confianza el procesador integrado Nios II en nuestros sistemas”.

Los ASIC HardCopy de Altera brindan a los clientes una ruta de migración de bajo costo, bajo riesgo y bajo consumo de energía para trasladar sus diseños de prototipos de FPGA a la producción en volumen. El uso de ASIC HardCopy hace que Thales sea tolerante a la perturbación de un solo evento (SEU) al mismo tiempo que proporciona compatibilidad pin-to-pin, funcional y de tiempo con los diseños de prototipos de FPGA.

El desarrollo de una versión crítica para la seguridad del procesador de núcleo blando Nios II de Altera es el resultado de una estrecha asociación y colaboración entre Thales, HCELL Engineering y Altera que se remonta a 2006. El paquete compatible con RTCA DO-254/Eurocae ED-80 del procesador integrado Nios II proporciona a los fabricantes de equipos de aviónica un microprocesador comercial listo para usar (COTS) que se puede implementar rápida y fácilmente en aviónica crítica para la seguridad. solicitud. Al aprovechar el procesador integrado Nios II en estos sistemas, los fabricantes pueden reducir significativamente el tiempo y los costos de desarrollo y eliminar la amenaza de la obsolescencia del procesador, al mismo tiempo que cumplen con los estándares de seguridad.

“El anuncio de hoy reduce significativamente la barrera de riesgo para los clientes que buscan implementar procesadores de núcleo blando en sistemas de aviónica críticos para la seguridad”, dijo Amr El-Ashmawi, gerente senior de marketing de la unidad comercial militar de Altera. “La certificación EASA del equipo de respaldo electrónico integrado de Thales destaca los importantes ahorros en costos, tiempo de desarrollo y riesgos que brindan los procesadores Nios II con certificación DO-254 de Altera”.

Acerca de la versión crítica para la seguridad del procesador Nios II

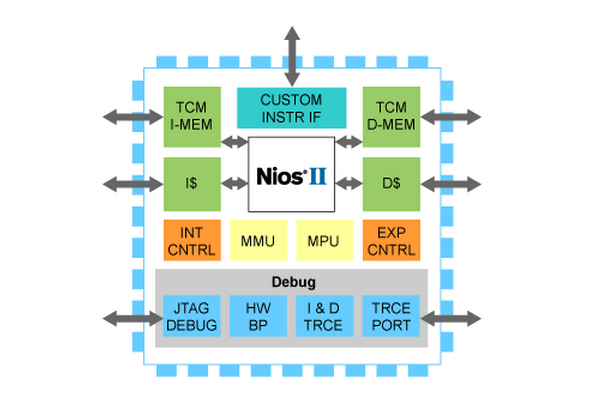

El procesador integrado Nios II de Altera es un microprocesador de software basado en FPGA de 32 bits configurable que se utiliza en una amplia gama de aplicaciones y mercados finales, incluidos los militares, aeroespaciales y de aviónica. La versión crítica para la seguridad del núcleo del procesador incluye el cumplimiento total de RTCA DO-254/Eurocae ED-80 e incluye el código fuente y documentos como el Plan para aspectos de certificación de hardware (PHAC), el Documento de diseño de hardware (HDD) y el Resumen de logros de hardware (HAS). Los diseñadores de hardware de aviónica que cumplen con el estándar DO-254 pueden aprovechar el núcleo del procesador de software Nios II mientras minimizan la obsolescencia del sistema, que generalmente tiene un ciclo de vida prolongado. El procesador integrado Nios II se puede implementar dentro de la cartera de Altera de FPGA de la serie Cyclone® y Stratix® y ASIC de la serie HardCopy.