El ADF7023-J es un chip 2FSK/GFSK/2FSK/GFSK/2FSK/GFSK/2FSK altamente integrado, de muy bajo consumo y alto rendimiento diseñado para operar en la banda de frecuencia de 902 MHz a 958 MHz que cubre la banda T96 del estándar ARIB de 950 MHz. Transceptor MSK/GMSK. Se admiten velocidades de datos de 1 kbps a 300 kbps.

El ADF7023-J es un chip 2FSK/GFSK/2FSK/GFSK/2FSK/GFSK/2FSK altamente integrado, de muy bajo consumo y alto rendimiento diseñado para operar en la banda de frecuencia de 902 MHz a 958 MHz que cubre la banda T96 del estándar ARIB de 950 MHz. Transceptor MSK/GMSK. Se admiten velocidades de datos de 1 kbps a 300 kbps.

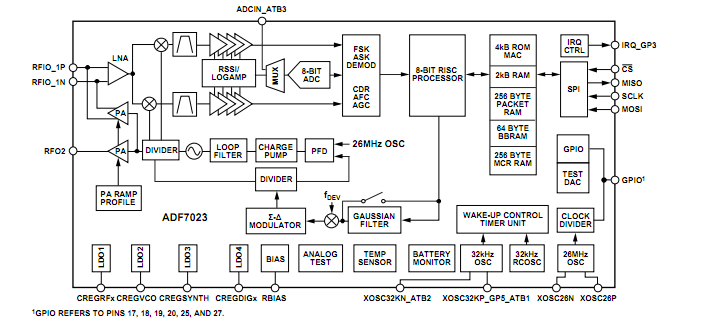

El sintetizador de RF de transmisión contiene un VCO y un bucle de bloqueo de fase (PLL) de N fraccional de bajo ruido con una resolución de frecuencia de canal de salida de 400 Hz. El VCO opera al doble de su frecuencia fundamental para reducir las emisiones espurias. Los anchos de banda del sintetizador de recepción y transmisión se configuran de forma automática e independiente para lograr un ruido de fase, una calidad de modulación y un tiempo de estabilización óptimos. La potencia de salida del transmisor es programable de −20 dBm a +13,5 dBm y tiene una función de rampa de megafonía automática para cumplir con las especificaciones de transitorios espurios. La parte tiene PA de un solo extremo y diferenciales, lo que permite la diversidad de antenas Tx.

El receptor es altamente lineal y logra especificaciones IP3 de -12,2 dBm y -11,5 dBm con ganancia máxima y mínima, respectivamente, y especificaciones IP2 de 18,5 dBm y 27 dBm con ganancia máxima y mínima, respectivamente. El receptor logra una especificación de bloque de interferencia de 66 dB con compensaciones de ±2 MHz y 74 dB con compensaciones de ±10 MHz. Por lo tanto, esta parte es muy tolerante a la presencia de interferencias en entornos espectralmente ruidosos. Este receptor cuenta con un nuevo bucle AFC de alta velocidad que permite que el PLL detecte y corrija errores de frecuencia de RF en los paquetes recuperados. Un esquema de calibración de rechazo de imagen pendiente de patente está disponible descargando un módulo de firmware de calibración de rechazo de imagen en la RAM del programa. Este algoritmo no requiere el uso de una fuente de RF externa y no requiere la intervención del usuario después del inicio. Los resultados de la calibración se pueden guardar en una memoria no volátil para utilizarlos la próxima vez que se encienda el transceptor.

Consulte la hoja de datos para obtener información adicional.

solicitud

- medición inteligente

- EEE802.15.4g

- automatización del hogar

- Gestión de procesos y edificios

- Red de sensores inalámbricos (WSN)

- cuidado de la salud inalámbrico