Agilent Technologies Inc. anunció hoy la última versión de su software de simulación, verificación y análisis RFIC, GoldenGate versión 2011.

Agilent Technologies Inc. anunció hoy la última versión de su software de simulación, verificación y análisis RFIC, GoldenGate versión 2011.

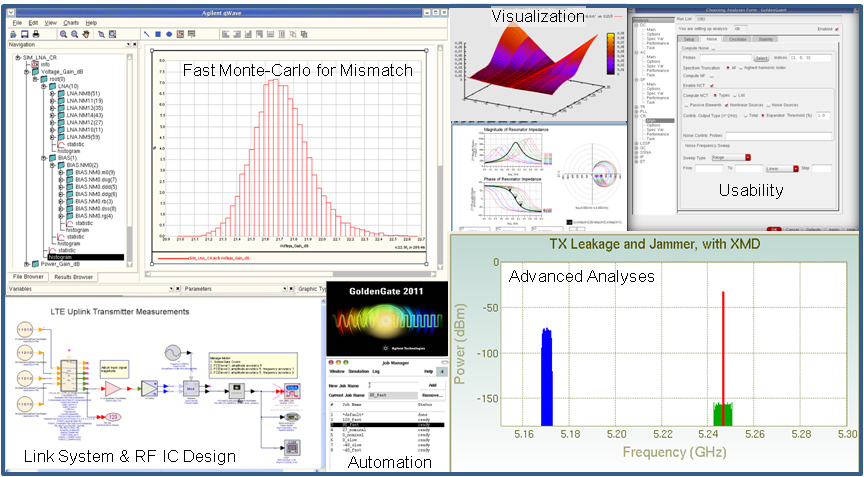

Esta versión amplía el liderazgo de Agilent en el diseño avanzado de RFIC de nodos con un rendimiento mejorado, un análisis de desajustes más rápido para aplicaciones analógicas y de RF, y una nueva interfaz gráfica de usuario fácil de usar. Esta versión también amplía el análisis RFIC del software para incorporar más fácilmente los efectos del paquete y la placa.

“Hay muchas formas de mejorar el rendimiento”, dice Paul Colestock, director de marketing y planificación de productos de la organización EEsof EDA de Agilent. “El enfoque de Agilent es proporcionar mejoras continuas en los circuitos que más les importan a nuestros clientes. GoldenGate 2011 se mantiene fiel a esa tradición”.

El software GoldenGate versión 2011 de Agilent ofrece las siguientes actualizaciones para el análisis de diseño de RF:

- El análisis de portadora mejorado aumenta significativamente la escalabilidad y el rendimiento en CPU multinúcleo, lo que amplía aún más el liderazgo de Agilent en el rendimiento de RF.

- Mejoras significativas en el rendimiento para el análisis de ruido de portadora y SSNA.

- Análisis rápido de atribución de rendimiento para diseñadores de RF y señales analógicas/mixtas, incluido el análisis de CC, CA y oscilador.

- El análisis mejorado de la envolvente del circuito de alta velocidad acelera la simulación de la ruta funcional de RF en más de un orden de magnitud y brinda un soporte más amplio para configuraciones de fuente centradas en RFIC para modelos que incluyen efectos de memoria.

- Opciones de convergencia de cristal mejoradas para reducir la frustración de la simulación del oscilador de cristal.

GoldenGate versión 2011 tiene muchas mejoras para la verificación de diseño inalámbrico. El análisis rápido de discrepancias, incluida la nueva compatibilidad con la herramienta Cadence Corner, acelera en gran medida la verificación de rutas funcionales y de bloques que los diseñadores de RFIC realizan todos los días sin comprometer la precisión.

El adlib actualizado para la biblioteca GoldenGate ahora incluye líneas de transmisión definidas por retardo y modelos de cable de unión estándar/definidos por el usuario de Philips-TU Delft. Permite a los ingenieros simular más diseños, incluido el paquete de RF y los efectos de la placa. Además, al cerrar el ciclo entre los diseñadores de sistemas y circuitos utilizando los nuevos enlaces y flujos de SystemVue y GoldenGate, los diseñadores pueden acelerar significativamente la verificación de los RFIC a nivel del sistema.

La versión 2011 de GoldenGate de Agilent mejora tanto la facilidad de uso de la herramienta como la productividad del usuario. Por ejemplo, una nueva interfaz gráfica de usuario en forma de árbol/pestañas para el entorno de diseño analógico de cadencia simplifica la configuración del análisis de RF y la selección de opciones/entorno.