La nueva familia LatticeECP4 es la cuarta generación de FPGA innovadores de bajo costo y bajo consumo con un motor de comunicación de propiedad intelectual por cable y potentes bloques DSP. La innovadora familia de FPGA LatticeECP4 es ideal para aplicaciones cableadas, inalámbricas, de video, industriales y de cómputo sensibles al costo y la energía. La nueva familia de FPGA LatticeECP4 presenta un SERDES 6G versátil para transmisión de datos de alta velocidad, un motor de comunicación MACO integrado para un procesamiento de protocolo eficiente, bloques DSP 7 veces más potentes para video e inalámbrico, interfaz de memoria DDR3 de 1066 Mbps, alta densidad chip de memoria y más. Hasta 250 000 elementos lógicos (LUT).

La nueva familia LatticeECP4 es la cuarta generación de FPGA innovadores de bajo costo y bajo consumo con un motor de comunicación de propiedad intelectual por cable y potentes bloques DSP. La innovadora familia de FPGA LatticeECP4 es ideal para aplicaciones cableadas, inalámbricas, de video, industriales y de cómputo sensibles al costo y la energía. La nueva familia de FPGA LatticeECP4 presenta un SERDES 6G versátil para transmisión de datos de alta velocidad, un motor de comunicación MACO integrado para un procesamiento de protocolo eficiente, bloques DSP 7 veces más potentes para video e inalámbrico, interfaz de memoria DDR3 de 1066 Mbps, alta densidad chip de memoria y más. Hasta 250 000 elementos lógicos (LUT).

innovación de alto rendimiento

SERIE 6G de alta calidad

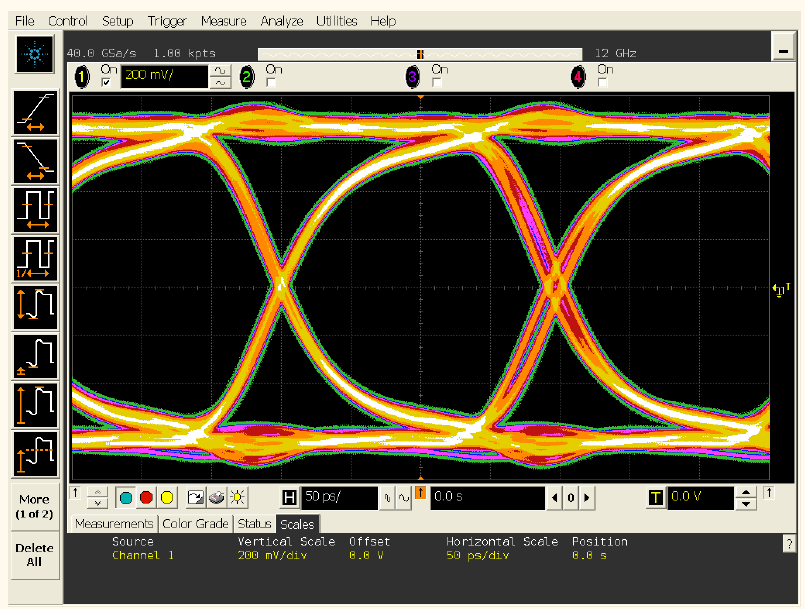

Los FPGA LatticeECP4 contienen hasta 16 canales SERDES de 6 Gbps que cumplen con CEI en paquetes de enlace de cable de bajo costo y paquetes flip-chip de alto rendimiento, lo que permite a los clientes implementar FPGA LatticeECP4 en aplicaciones de backplane de larga distancia y de chip a chip. desplegar a El canal SERDES puede operar a velocidades de 155 Mbps a 6 Gbps y está certificado para muchos protocolos cableados, inalámbricos y de diseño de sistemas (10 Gigabit Ethernet, 1 Gigabit Ethernet, SGMII, XAUI, RXAUI, PCI Express 2.1, SRIO). 2.0, CPRI. Para obtener más información, visite la página de SERDES de baja potencia de LatticeECP4.

Motor de comunicación MACO 10 veces más eficiente

El potente motor de comunicación MACO es un bloque de propiedad intelectual (IP) cableado. MACO significa “costo de acceso múltiple optimizado” y se puede acceder a estos motores desde 6G SERDES o E/S de alta velocidad. La cartera de motores de comunicaciones LatticeECP4 incluye soluciones para PCI Express 2.1, múltiples MAC de 10 Gigabit Ethernet, MAC de Ethernet de tres velocidades, así como E/S rápida en serie (SRIO) 2.1. Los FPGA LatticeECP4 incorporan los bloques IP duros de mayor densidad de la industria para una comunicación eficiente. Las FPGA LatticeECP4 pueden incorporar hasta 22 motores de comunicación, mientras que las FPGA de “rango medio” de la competencia solo tienen PCI Express y algunos bloques MAC IP de Ethernet. Para obtener más información, visite la página del motor de comunicación LatticeECP4 MACO.

Bloque DSP 7 veces más potente

La familia LatticeECP4 cuenta con un revolucionario y potente bloque de procesamiento de señales digitales (Power sysDSP) que ofrece 7 veces el rendimiento de los FPGA de la competencia. Estas innovaciones permiten a los clientes implementar complejos sistemas inalámbricos de múltiples antenas (4×4 MIMO 40 MHz) y algoritmos de procesamiento de video de alto rendimiento en plataformas FPGA de bajo costo y bajo consumo. Un bloque LatticeECP4 DSP con todas las funciones incluye un multiplicador de 18×18, ALU, árbol de sumador ancho y cadena de transporte para cascada. Además, se pueden conectar en cascada hasta 576 multiplicadores para crear filtros complejos. Para obtener más información sobre el poderoso LatticeECP4 FPGA, visite la página de tecnología LatticeECP4 DSP.

E/S rápida con CDR incorporado

Las FPGA LatticeECP4 cuentan con E/S de sistema diferencial (GIGA sysIO) un 50 % más rápidas que la generación anterior de la familia LatticeECP3. GIGA sysIO funciona a velocidades de hasta 1,25 Gbps. Con circuitos integrados de recuperación de datos de reloj (CDR), GIGA sysIO se puede utilizar para implementar una gran cantidad de interfaces seriales Gigabit Ethernet y SGMII. GIGA sysIO CDR ahorra 6G SERDES para otras aplicaciones de alta velocidad. La interfaz de memoria DDR3 de 1066 Mbps de bajo costo y alto rendimiento reduce el costo del sistema. Para obtener más información sobre la amplia gama disponible, visite la página de E/S de alta velocidad de LatticeECP4.

Principales características

- Tejido FPGA de bajo costo y bajo consumo

- Proceso de baja potencia de 65 nm con estructura de tabla de consulta (LUT) de 4 entradas

- Densidad lógica de 30K a 250K LUT

- RAM de bloque integrada (EBR) de hasta 10,6 Mbit

- RAM distribuida de hasta 600 Kbit

- SERDES integrado rápido

- SERDES 6G que cumple con CEI en un paquete de bajo costo

- Hasta 16 canales a velocidades de datos de 155 Mbps a 6 Gbps

- Bajo consumo de energía de 175 mW por canal a 6 Gbps

- Preempatía incorporada y ecualización de retroalimentación de decisiones (DFE)

- Motor de comunicación MACO

- Hasta 22 motores IP cableados para protocolos populares

- PCIe 2.1 x4, 10 GbE, MAC de tres velocidades, SRIO 2.1

- Interfaz perfecta con SERDES/PCS y fabric

- Herramienta de diseño de software de planificación de sistema flexible

- Potente bloque DSP (Power sysDSP)

- Bloque DSP con todas las funciones con multiplicar, acumular, sumar, restar

- Hasta 576 multiplicadores 18×18 en cascada con ALU y árboles sumadores anchos

- Booster patentado y lógica pre-agregador aumenta el rendimiento en 4 veces

- Cree filtros complejos para aplicaciones inalámbricas y de video

- E/S de alta velocidad

- E/S diferencial (GIGA sysIO) con velocidad de datos de hasta 1,25 Gbps

- E/S serie Gigabit con CDR (Circuito de recuperación de datos de reloj) integrado

- Hasta 40 CDR incorporados

- Interfaz de memoria DDR3 de 1066 Mbps

- Búfer sysIO flexible

- LVCMOS 33/25/18/15/12 y PCI

- SSTL33/25/18/15 y HSTL15 y HSTL18

- LVDS, Bus LVDS, RSDS, MLVDS y LVPECL

- cambiador de nivel de voltaje

- sysCLOCK PLL y DLL

- 8 DLL y 8 PLL por dispositivo

- Amplia gama de opciones de E/S de paquetes y usuarios

- Hasta 512 pines de E/S de usuario

- Interfaz 6G de corto alcance (SR) en paquete fpBGA wirebond de bajo costo

- Interfaz 6G Long Reach (LR) en paquete fcBGA flip-chip de alto rendimiento

- Sin plomo y compatible con RoHS

- Opciones de configuración avanzadas

- Configurado con flash de arranque SPI o flash de modo de ráfaga paralelo

- El arranque dual proporciona una copia de seguridad de la configuración

- Cifrado AES de 128 bits

- Actualizaciones en vivo con tecnología TransFR

aplicación de destino

Con interfaces de datos de alta velocidad, motores de comunicación premium y potentes bloques DSP, las FPGA LatticeECP4 de próxima generación están optimizadas para una amplia gama de aplicaciones de procesamiento de video y comunicaciones alámbricas e inalámbricas. Las características únicas de LatticeECP4 FPGA para estas aplicaciones se analizan a continuación.

acceso inalámbrico

Los FPGA LatticeECP4 tienen muchas características únicas para ayudar a los clientes a diseñar cabezales de radio remotos (RRH) multimodo y estaciones base 4G. Un bloque DSP 7 veces más potente facilita la linealización de señales de múltiples antenas. LatticeECP4 es la única FPGA que ofrece interfaces CPRI y SRIO 2.1 variantes de baja latencia para aplicaciones inalámbricas. La interfaz SRIO 2.1 se implementa en el eficiente motor de comunicación MACO.

acceso por cable

Con un motor de comunicación MACO, una amplia cartera de SERDES y GIGA sysIO de alta calidad con circuitos CDR incorporados, el LatticeECP4 es la opción perfecta para construir backhaul inalámbrico de última generación, acceso por cable, conmutadores y enrutadores, y sistemas informáticos y de almacenamiento. Una plataforma ideal. Las FPGA LatticeECP4 incorporan hasta 40 circuitos CDR, que se pueden usar para implementar interfaces Gigabit Ethernet y SGMII usando una gran cantidad de pines GIGA sysIO. Con CDR incorporado y 6G SERDES/PCS, GIGA sysIO se puede utilizar para construir una plataforma de comunicación de alta densidad de puertos.

borde de video

Los FPGA LatticeECP4 cuentan con una combinación ideal de recursos para las principales aplicaciones de transmisión de video, códec, análisis y procesamiento. SERDES 6G de bajo jitter y el motor de comunicación MACO incorporado permiten la captura de alta fidelidad y la transmisión de datos de video a larga distancia. Los potentes bloques DSP permiten la implementación rentable de algoritmos de procesamiento de video complejos. Las interfaces de memoria DDR3 de alta velocidad y las interfaces de E/S diferenciales permiten el procesamiento simultáneo de múltiples canales de video. Estos componentes básicos de LatticeECP4 FPGA permiten a los clientes diseñar rápidamente cámaras de video industriales, cámaras de vigilancia, transmisión, pantallas, sistemas de imágenes médicas y sistemas de entretenimiento automotriz.