Los PCM1753/54/55 son circuitos integrados monolíticos CMOS que contienen un convertidor estéreo de digital a analógico y circuitos de soporte en un pequeño paquete SSOP de 16 pines.

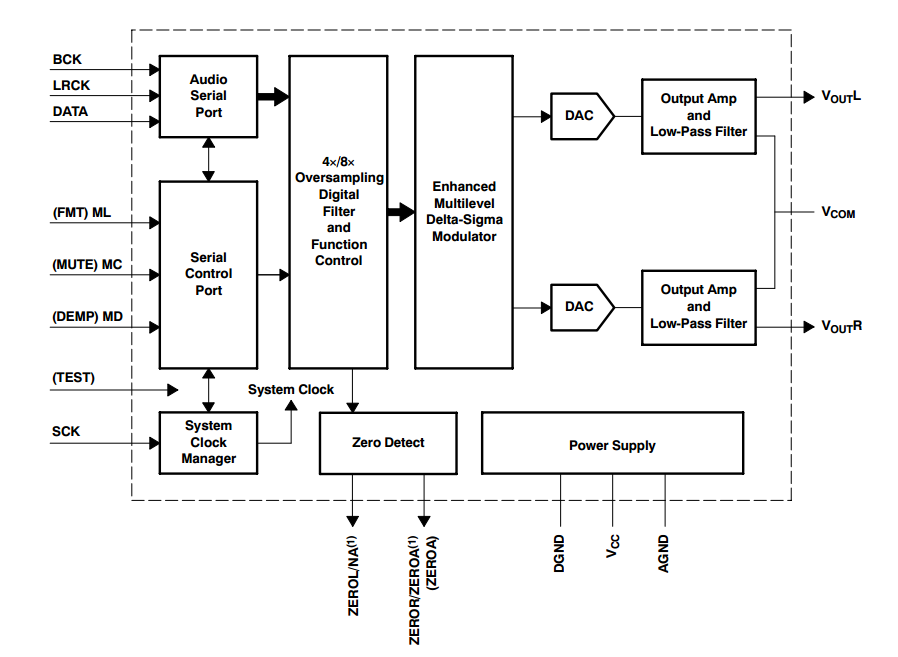

Los PCM1753/54/55 son circuitos integrados monolíticos CMOS que contienen un convertidor estéreo de digital a analógico y circuitos de soporte en un pequeño paquete SSOP de 16 pines. El convertidor de datos utiliza la arquitectura delta-sigma multinivel mejorada de TI, que emplea modelado de ruido de cuarto orden y cuantización de amplitud de 8 niveles para un rendimiento dinámico superior y una mayor inmunidad a la fluctuación del reloj. El PCM1753/54/55 acepta formatos de datos de audio estándar de la industria de datos de 16 a 24 bits y proporciona una interfaz simple para DSP de audio y chips decodificadores. Se admiten frecuencias de muestreo de hasta 200 kHz. Se puede acceder a un conjunto completo de funciones programables por el usuario a través de un puerto de control en serie de 3 hilos que admite la funcionalidad de registro de escritura.

Los pines PCM1753/55 son compatibles con PCM1748, PCM1742 y PCM1741 excepto el pin 5.

teoría de operación

La sección delta-sigma del PCM1753/54/55 se basa en un cuantificador de amplitud de 8 niveles y un modelador de ruido de cuarto orden. En esta sección, convertimos los datos de entrada sobremuestreados al formato delta-sigma de 8 niveles. En la Figura 32 se muestra un diagrama de bloques de un modulador delta-sigma de 8 niveles. Este modulador delta-sigma de 8 niveles tiene ventajas en términos de estabilidad y sensibilidad a la fluctuación del reloj sobre el modulador delta-sigma común de 1 bit (2 niveles). . La tasa de sobremuestreo del modulador delta-sigma combinado y el filtro de interpolación es de 64 fS. El rendimiento teórico del ruido de cuantificación de un modulador delta-sigma de 8 niveles se muestra en las Figuras 33 y 34 de la hoja de datos. La arquitectura delta-sigma multinivel mejorada también se beneficia de la sensibilidad a la fluctuación del reloj de entrada gracias al cuantificador multinivel con sensibilidad a la fluctuación simulada. Se muestra en la Figura 35 de la hoja de datos.

característica

- resolución de 24 bits

- Rendimiento analógico (VCC = 5 V)

- Rango dinámico: 106dB

- SNR: 106dB, típico

- THD+N: 0,002 %, típico

- Salida a escala completa: 4 VPP, típico

- Filtro digital de sobremuestreo 4×/8×:

- Atenuación de banda suprimida: –50 dB

- Ondulación de banda de paso: ±0,04 dB

- Frecuencia de muestreo: 5kHz a 200kHz

- Reloj del sistema: 128 fS, 192 fS, 256 fS, 384 fS, 512 fS, 768 fS, 1152 fS (con detección automática)

- Control de software (PCM1753, PCM1755):

- Acepta formatos de audio de 16, 18, 20 y 24 bits: estándar, I2S y justificado a la izquierda

- Atenuación digital: 0 dB a –63 dB, 0,5 dB/paso

- desacentuación digital

- Roll-off de filtro digital: agudo o lento

- silencio suave

- Bandera cero para cada salida

- Indicador cero de salida de drenaje abierto (PCM1755)

- Control de hardware (PCM1754):

- I2S y palabras de 16 bits, justificado a la derecha

- Desacentuación digital de 44,1 kHz

- silencio suave

- Indicador cero para la salida común de los canales L y R

- Fuente de alimentación: fuente de alimentación única de 5V

- Paquete SSOP pequeño de 16 pines, sin plomo

solicitud

- receptor de audio y video

- reproductor de películas en DVD

- Tarjeta adicional de DVD para PC de gama alta

- reproductor de audio DVD

- receptor de televisión de alta definición

- sistema de audio del coche

- Otras aplicaciones que requieren audio de 24 bits